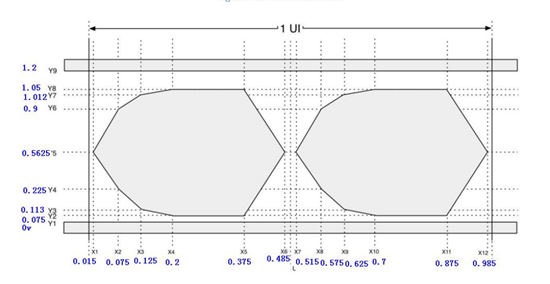

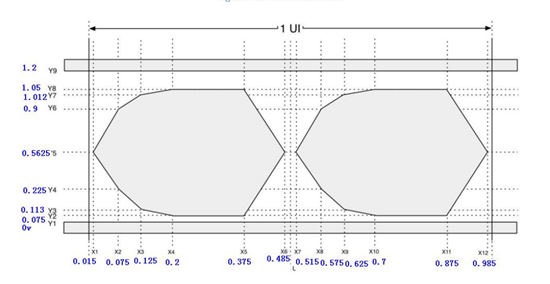

信号最大速率1MHz,由FPGA 3.3V IO输出,需要将其振幅转换成1.1V,输出阻抗为50Ω,支持高阻输出...转出信号眼图如下

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

信号最大速率1MHz,由FPGA 3.3V IO输出,需要将其振幅转换成1.1V,输出阻抗为50Ω,支持高阻输出...转出信号眼图如下

看了下,1路的话支持1.1V低电压的器件还没有,可参考carter提供的两款,带方向控制位的4bit的SN74AVC4T234和不带方向控制位的txb0302。

关于你提到的输出阻抗,估计你的应用对阻抗匹配有要求, 这样的话,可能只能通过仿真SN74AVC4T234或者txb0302和其他器件的IBIS model验证下信号的完整性了。

一般CMOS或者TTL逻辑器件做源端阻抗匹配比较困难,因为工艺的原因,匹配电阻很不准确,需要调试时测量并调节外部电阻值。