性能要求:

1、Memory芯片:时钟CLK =200MHz,数据8位DATA0~7工作在DDR模式,即400MHz,所有线电平标准是1.8V逻辑;FPGA端电平标准是2.5V,且以固定不能更改,现想实现FPGA对Memory进行控制,需要电平转换

望能推荐一款电平转换芯片实现两侧的连接。

前提:FPGA板是现成开发板,需要做子卡连到开发板的FMC上。开发板FMC接口电平标准都是2.5V的不能更改。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

性能要求:

1、Memory芯片:时钟CLK =200MHz,数据8位DATA0~7工作在DDR模式,即400MHz,所有线电平标准是1.8V逻辑;FPGA端电平标准是2.5V,且以固定不能更改,现想实现FPGA对Memory进行控制,需要电平转换

望能推荐一款电平转换芯片实现两侧的连接。

前提:FPGA板是现成开发板,需要做子卡连到开发板的FMC上。开发板FMC接口电平标准都是2.5V的不能更改。

你好,我想知道SN74LVC8T245貌似速度不高,不能支持200MHz吧,而且8个通道的延迟貌似也不确定,

方向控制也会有延迟,请您在帮忙给推荐一下其他的有没有差不多的。

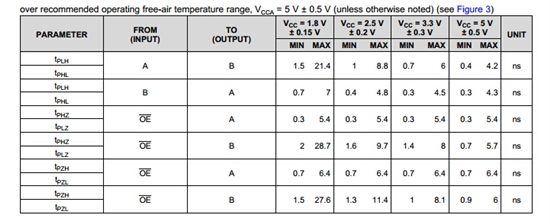

哦 不好意思,是的SN74LVC8T245不能支持200Mhz的速度,不过我看了下1.8V转2.5V的8位电平转换器件中,貌似没有能够支持400MHz这么大速度的呢。像AVC系列的传输延迟时间低,SN74AVCH8T245:

Max Data Rates:

320 Mbps (VCCA >=1.8 V and VCCB >= 1.8 V)

170 Mbps (VCCA <=1.8 V or VCCB<= 1.8 V)

对于相同输入信号来说,不同通道间的传输延迟是一致的。传输延迟时间越短,表明数据的data rate越高。

但同一芯片的传输延迟,控制信号的传输延迟和数据信号的传输延迟时间可能是不一致的。

是的,传输速率是和传输延迟,输入信号的灵敏度,上升沿和下降沿的速度等多种因素有关的,通常我们可以用Tpd最大值(+10%)来作为数据的最大传输延迟时间,计算的时候用它们的倒数来估算最大传输速率。sheng mu 说:数据的速度跟传输延迟有关吗还?

我理解的是传输速度跟芯片的带宽有关系,或者跟芯片的压摆率有关系,而传输延迟只是通道的相位延迟,不知道我理解的对不对,还望指教。

LSFxx的-3dB带宽为600MHz,200MHz应该是没问题的,关于上拉电阻的确定,是当内部晶体管导通时限制电流为15mA,所以可根据公式1来计算出不同电压情况下的上拉电阻值,因此上拉电阻越大,晶体管导通时流经的电流越小,应该是没问题的。你的应用建议还是申请样片实际验证下。

您好,能不能具体解释一下,传输延迟是如何影响传输速率的。这个问题一直想不明白。