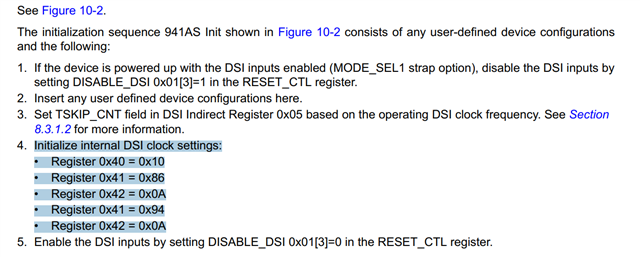

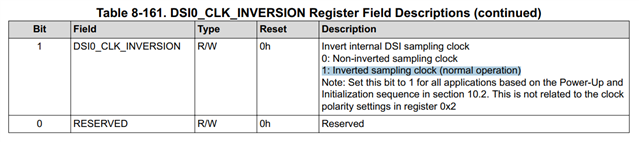

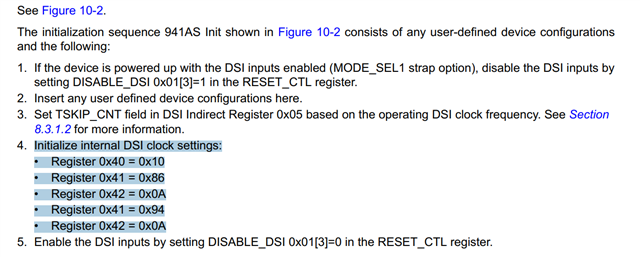

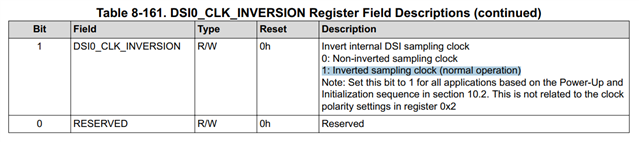

在941的datasheet 10.2 Power-Up and Initialization 节中,上电初始化的第4步是设置 internal DSI clock,并且针对所有应用都设置成"Inverted sampling clock",请问这是必要的操作吗?这样设置的原因是什么?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

在941的datasheet 10.2 Power-Up and Initialization 节中,上电初始化的第4步是设置 internal DSI clock,并且针对所有应用都设置成"Inverted sampling clock",请问这是必要的操作吗?这样设置的原因是什么?

原因如下:

应始终执行此操作。

在941A DSI接收器块中发现了采样余量问题,特别是在DSI数据通道0上。 错误采样的数据可能导致显示屏上出现视觉像素错误和某些设备上出现DSI CRC错误。 可通过反转DS90UH941A-Q1 DSI接收器块内的DSI采样时钟来校正DSI采样余量。 反转采样时钟为所有设备和数据表操作条件的采样和保持窗口增加了足够的余量。 在启用DSI接收器之前,应在初始化期间应用此变通办法。

同时,将其移动到内部。

This override should always be implemented.

A sampling margin issue was identified within the 941A DSI receiver block, specifically on DSI data lane 0. This mis-sampled data can lead to visual pixel errors on the display and DSI CRC errors on some units. The DSI sampling margin can be corrected by inverting the DSI sampling clock within the DS90UH941A-Q1 DSI receiver block. Inverting the sampling clock adds sufficient margin to the sample and hold window across all units and datasheet operating conditions. This workaround should be applied during initialization before enabling the DSI receiver.

Also, moving this to internal.