Other Parts Discussed in Thread: CDCE62005

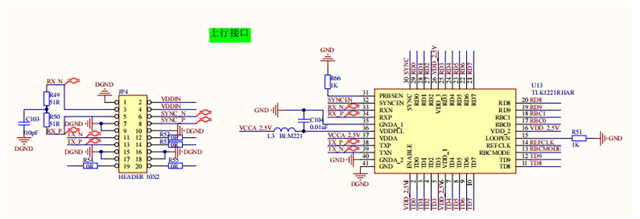

上图是我的硬件原理图设计。

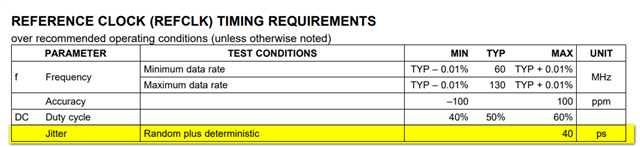

使用FPGA程序驱动TLK1221芯片,RBCOMDE=1,REFCLK=100MHz。

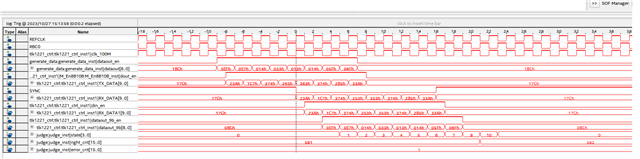

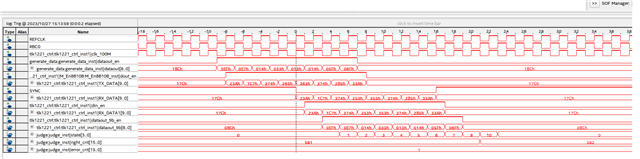

我写了一组测试数据,原码为EF E7 14 33 13 14 5F 6F,将它通过编码模块,编码为23A 1C7 374 253 353 374 2B5 33A。编码后的数据输入到TLK1221管脚TD0--TD9。在上图JP4接插件中,我将TXP,TXN分别接到RXP,RXN管脚,随后通过quartus prime中signaltap抓取RD0-RD9观察。抓到的波形如下:

TX_DATA和RX_DATA是相等的,接收和发送都没有问题。我循环测了一万次,都正确。

但是在实际应用过程中,板卡1的数据需要发送到板卡2,即板卡1的TX需要接到板卡2的RX。于是我通过双绞线将板卡1的TX接到板卡2的RX端,两个 板卡的GND连通。这个时候就会出现问题:

同样测试了一万次,正确的为9072次,错误928次。

对上面这个问题我感到很困惑,在FPGA程序中我增加了时钟约束,没有一点改善,想请教一下应该如何着手,请求给我点建议以帮助我解决这个问题。