简短答案:对于具有总线保持电路的器件,不建议使用外部上拉/下拉电阻器。

说明:

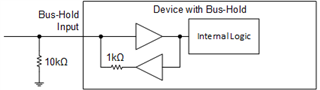

具有总线保持电路时,只要总线保持电路处于与电阻器电源相反的状态,上拉或下拉电阻器就会构成一个分压器。

例如:

对于典型总线保持电路,输出电阻约为 1kΩ。如果输入端有一个 10kΩ 下拉电阻器,并且没有以其他方式主动驱动线路,则可能存在两种状态:

(1) 总线保持电路处于低电平状态,这时没有问题。

(2) 总线保持电路处于高电平状态,现在输入电压会被拉低至约 0.9 * VCC。

如果您不关心输入处于什么状态,那么 #2 不是什么大问题,但是如果您打算将下拉电阻器置于低电平状态,那么除非该电阻器非常小(即小于 1kΩ),否则您可能会发现它不起作用。

如果是这种情况,最好不要使用总线保持电路。

您可以通过以下应用手册深入而详细地了解总线保持电路及其工作原理:慢速或浮动 CMOS 输入的影响的第 6 节。