Other Parts Discussed in Thread: SN74LVC1T45

请教,SN74LVC8T245器件的第2pin DIR是否可以通过连接第23&24Pin拉高吗?

电路如下,需要实现的功能是左右两边信号电平切换,其中LOCK信号是B Port输入,A port输出;其他信号据需要A port 输入,B Port 输出。

其中LOCK信号是Open Drain模式的检测信号,正常上拉到3.3V,异常是拉致GND。

请协助确认一下图纸设计是否OK?

THS!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

请教,SN74LVC8T245器件的第2pin DIR是否可以通过连接第23&24Pin拉高吗?

电路如下,需要实现的功能是左右两边信号电平切换,其中LOCK信号是B Port输入,A port输出;其他信号据需要A port 输入,B Port 输出。

其中LOCK信号是Open Drain模式的检测信号,正常上拉到3.3V,异常是拉致GND。

请协助确认一下图纸设计是否OK?

THS!

Hi Amy;

正常情况下,除了LOCK信号外其他都是来至Master的输出信号,通过SN74LVC8T245进行电压切换输送给slaver;Lock信号是slaver输出,通过SN74LVC8T245进行电压切换输送给Master;并且只有当LOCK信号为L时才需要从slaver传送到Master,正常情况时通过上拉电阻置H;如上设计将DIR连接到LOCK信号上,是否可以实现这种需要求?

并且只有当LOCK信号为L时才需要从slaver传送到Master,正常情况时通过上拉电阻置H;

如果您只需要LOCK信号为L时从B端到A端,并且LOCK 为OD接口,那么LOCK 信号您可以不经过电平转换芯片,将其上拉到1.8V输出接Master,这样主从间电平也是兼容的,即LOCK高电平时被上拉至1.8V,输出低电平时Master可以检测到。

还有其他3.3V接口需要检测LOCK信号吗?没有的话,我认为可以将LOCK pin 上拉到1.8V,因为它是OD接口,虽然其datasheet 推荐上拉到3.3V。

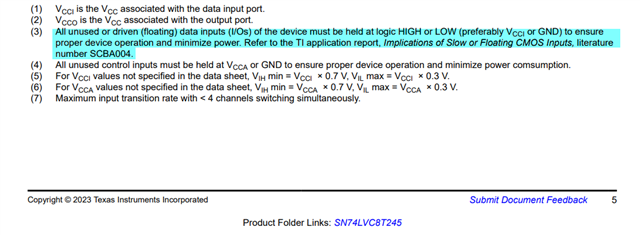

我不建议你这样用是因为在LOCK为低电平时,B端的其他信道相当于浮空状态,SN74LVC8T245不允许这样用:

Implications of Slow or Floating CMOS Inputs (Rev. E)

如果你使用的设备介意上拉到1.8V的话,建议加一个单通道的电平转换芯片SN74LVC1T45