We plan to use SN74AVC32T245 for 100MHz operating clock parallel interface, connecting to Xilinx FPGA HP bank LVCMOS1.8V IO and an ASIC with LVCMOS 3.3V.

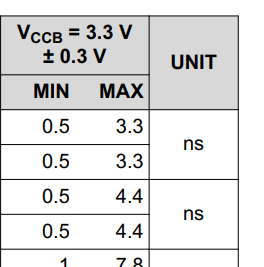

We noticed in the datahsheet it claimed 3.3V to 1.8V translate genrates 0.5-4.4ns Propagation delay and the oppsited direction generates 0.5ns-3.3ns.

I'd like to consult what factor contribute most to the the range of propagation delay?

Is that temperature and output load capacitor? Since I see most of the datahsheet have note that this range is based on operating temp range.

![]()

And I also saw the curve, if given fixed temperature, C load = 10pf increse to 60pf result in about 1ns PPD delay increase.

So in other word, say we are using 6 chips x 32 bit, we are care about the diverse between channel to channel and component to component.

If we are given fixed working temperature, and the same type connected I/O (e.g., all is connected to FPGA same bank same type I/O), and similar PCB trace routing.

Can we say we won't have any significant PPD diversity within channels, and components (much smaller thant the range such as 0.5ns-4.4ns)? If yes ,could you suggest how much is the diversity in this case?

You can answer me either in Chinese or English ,thanks much!