Other Parts Discussed in Thread: INA281

工具/软件:

大家好!

我有关于 INA281的问题。

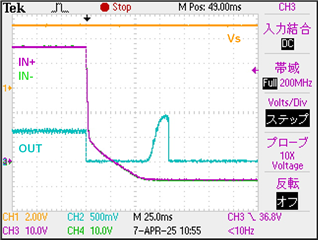

IN+和 IN-上的电压下降后、OUT 引脚会输出电压。

为什么会发生这种情况?

此致、

Ishiwata

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

尊敬的 Holly:

我很抱歉迟来的答复。

感谢您的答复。

我对 INA281A 有两个问题。

请您回答一下。

(1)当 INA281A 输入引脚 IN+和 IN-都处于相对于 GND 的高阻抗状态时、这些引脚的电压是否可能会降至约-8V?

(2)如果上述问题的答案是肯定的、那么在 IN+和 IN-都转换为-8V 电压的过程中、IN+和 IN-偏置电流的平衡是否可能失去、从而导致输出端产生几个100mV 的电压?

我来解释一下这些问题的背景。

我之前问过这个问题、得到的回答是、只要使用单电源 INA281A、IN+和 IN-引脚的电势绝不会降至 GND 以下。

我当前使用的电路在电流检测电阻的高侧有一个 FET、用于控制电源的开/关。

此外、电流检测电阻和负载之间还有一个二极管、以防止回流。

当我使用 PSPCIE for TI 对该电路进行仿真时、当 FET 关闭时、IN+和 IN-处的电压为-8V。

由此、我假设 IC 内部有一个电荷泵电路、并且当 IN+和 IN-处于共模高阻抗状态时、它们偏置为大约-8V。 这是正确的吗?

在客户测试中、在 FET 关断几十毫秒后观察到了几百 mV 的脉冲信号。 (上一篇文章中显示的波形。)

为了确定原因、我提出了一个假设。

当 IN+和 IN-引脚转换为-8V 时、两个引脚的偏置电流都存在差异。

我认为这通过安装用于滤波的1.2kΩ 电阻器转换为电压、即使没有电流流过电流检测电阻、输出引脚上也会产生高电压。

这不是在模拟中重现的。

我的假设正确吗?

此致、

Ishiwata

尊敬的 Holly:

感谢您的支持。

我会回应你的查询。

这种情况下的感测电压是多少?

=>当我对电路进行仿真时、我观察到在 FET 导通期间 IN+和 IN-之间存在32mV 的电压。

在使用实际器件时、我观察到 FET 导通期间 INA281A 输出的输出电压约为500mV。

它估算了25mV 的输入电压。

输入引脚相对于地处于高阻抗状态是什么意思?

=>当 FET 关断时、电源与感测电阻之间的阻抗较高、可能为兆欧量级。

同时、检测电阻和通过二极管的 GND 与负载之间的阻抗非常高(可能是

寄生电容)、只要 IN+和 IN-引脚由于二极管而在接地路径下偏置、

用于滤波的1.2k Ω 电阻非常大。 DS 的第7.1.2节讨论了输入滤波、建议将这些电阻器采用

不超过10欧姆。 我建议参考该部分、因为该部分说明了这些电阻器如何导致输入偏置电流不匹配。

=>感谢您的声音建议。 我将遵循您的建议。

就电压变为-8V 而言、让我来研究一下并返回给您。

=>期待您的回答。

此致、

Ishiwata

Ishiwata,

我不能说这是否正确:

由此、我假设 IC 内部有一个电荷泵电路、并且当 IN+和 IN-对共模处于高阻抗状态时、它们偏置为-8V 左右。 这是正确的吗?

但是、我认为您的假设是有道理的、我想、如果您减少输入滤波电阻器、这应该有助于在您的 VCM 下降时产生意外输出。

但同样、这个-8V VCM 违反了建议的运行条件、因此我无法确定这是否会解决该问题。

建议您在这些引脚未使用时将其置于运行规格范围内的已知状态。

BR、

Holly