线程中讨论的其他部件: REF3230, OPA2364, TINA-TI, OPA364, OPA363

我打算使用PGA112放大器来测量具有宽动态范围的电压。 要测量的峰值电压为60 V,使用100k / 4.7K电阻分压器将电压扩展到< 3V,并根据应用情况进行低通。 PGA112的输出随后将通过输出滤波器到达Piccolo或Delfino UC的12位ADC。

应用详细信息:这用于在BLDC电机控制器中感应相位电压,在该控制器中,控制器可与各种总线电压(Vbus = 6V - 60V)配合使用, 并且相位电压将在0 V和0 <占空比< 1的占空比*Vbus之间的0 - 500 Hz变化。

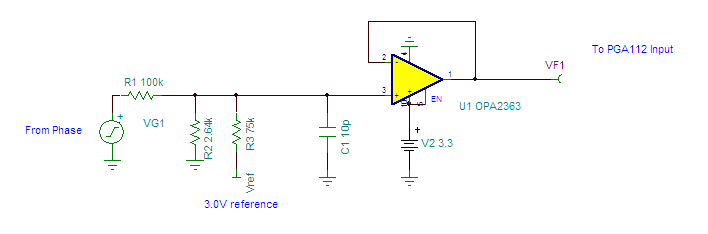

应用程序将使用PGA的增益来调整Vbus的变化;例如,在6V运行时,将使用8的增益。 但是,如果可能,我不打算动态更改增益(在电压连续读数之间)。 因此,在给定增益下,会出现PGA/ADC组合的可用动态范围问题。 实际上,ADC的标称分辨率为3.3V/2^12 = 0.8 mV/计数,但底部50 mV = 62计数无法区分。 如果我的输入在0V至100 mV之间变化(对于低占空比时的标度相电压非常合理),则输出的整整一半被截短且难以区分。

问题1:我在这里应该采取不同的方法来解决这个问题,无论是使用PGA112还是使用不同的部件? 我考虑使用无放大器增益,而是使用单端到差动放大器和Piccolo/Delfino ADC的16位模式,但出于各种原因,这不是理想的选择。

问题2:如果我继续使用PGA112,我可以将Vref设置为100 mV来偏移输出吗? 我知道这会限制我的增益为2+(因为Vref对增益=1没有影响),并略微限制我的输出范围(从100 mV到DVdd - 50 mV)。 我没有其他影响吗? 数据表讨论了Vref=GND和Vref=AVdd/2案例,但不讨论一般案例。

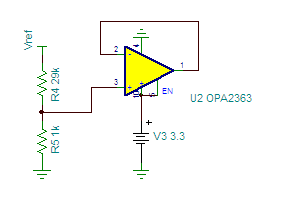

问题3:获得此范围内的参考电压(具有必要的电流源/吸收器要求)的最合适方法是什么? 我希望Vcal有可用的REF3230;我应该缓冲这种情况,电阻除以30,然后重新缓冲吗? OPA2364是否适用于此处的两个缓冲阶段? 4个PGA112共享第二个缓冲区的输出(100 mV参考电压)是否可以接受? (OPA2364的输出电流=45 mA >> 4x PGA112参考电流=4*2 mA。)

问题4:是否有PGA112的PSPICE/TINA-TI型号可用,以便我可以自己回答这些问题?