主题中讨论的其他器件: CDCE925

你好

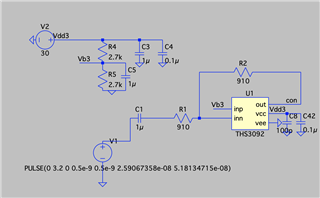

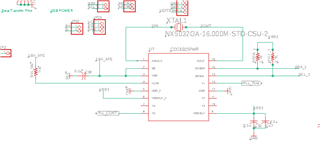

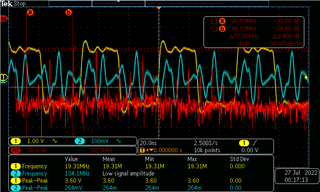

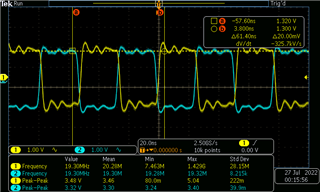

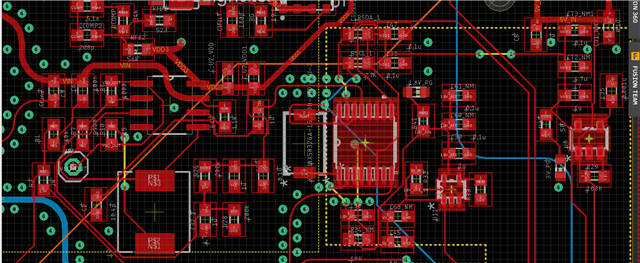

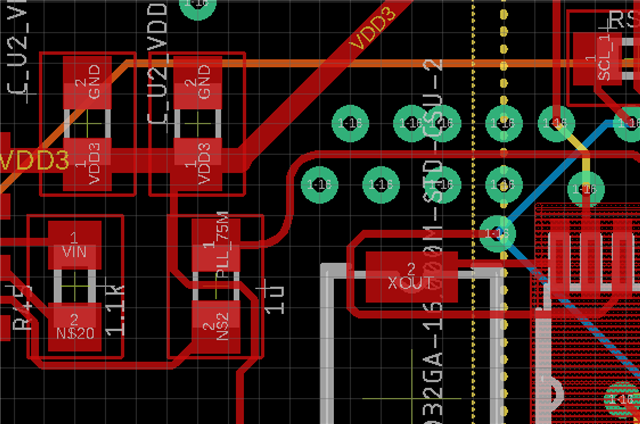

我正在使用 CDCE925PWR 生成19.3Meg 赫兹方波。 以馈入此 THS3092。 只要我打开运算放大器、我就会在电路中的任何地方看到、我拥有的每个直流输入都有260mV 峰值电压。 我有来自墙上适配器的5V 输入、用于进入3.3V LDO 和1.8V LDO。 我在电路中的任何地方都能看到这一点(图3)。 我运行 FFT、其频率分量是19.3Meg 赫兹的倍数。 我能够在没有这种波动的情况下操作 PLL 并生成该方波、但当我将其连接到 THS3092时、我会看到这种类型的波动。 在图4中、我得到了正确的输入和输出波。 我真的很困惑为什么会发生这种情况。 我在这个问题上已经呆了几个星期了、您能帮我解决吗?

谢谢你