大家好

如 OPA855的数据表中所示、GBW 为8G、 但实际上该参数有一定的偏差、例如±15%。 在我要 进行一些最坏情况仿真分析时、如何更改 OPA810 SPICE 模型中的 GBW。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

开环增益不恒定、但取决于许多因素。 其中一个是负载电阻、例如:

Kai

尊敬的 Sam:

我们发现 、我们最近 的运算放大器的输出振荡更加严重。 通过交叉测试 、我们确认 这批芯片可能存在一些问题。 我们怀疑 OPA855中 GBW 的偏置。

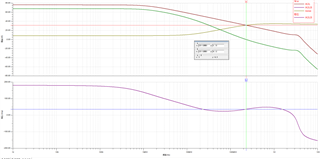

根据运算放大器的稳定性分析、相位裕度仅为36.12°、 但振荡的振幅是我们可以接受的。因此、我想 这一批 OPA855的主极点频率已经向前移动、导致相位裕度下降、因此 我们最近 的运算放大器的输出振荡更加严重。

有鉴于此,我想知道不同批次芯片的主极偏差以及如何进行仿真。

最棒的

Zhiyao 您好、

仅更改一个参数即可修改 GBW、这是一种过于简单的假设。 这些现代 TI 的 Spice 模型极其复杂且进步。

最好的方法是设计电路、使相位裕度具有很大的余量。 这比尝试修改 Spice 模型更巧妙。

仅36°的相位裕度太小。 请展示您的原理图、以便我们可以尝试提高相补角。

还请记住、不正确的探测也可能会导致不稳定。 Instabilty 还可能是布局不良(实心接地层、杂散电容过大、铜轨过长等)、电源电压去耦不良以及容性负载过大的增加造成的。 因此、我们需要查看原理图、布局和设置照片、以提供良好的帮助。

Kai

Zhiyao、如果没有原理图、很难对此进行说明-但是

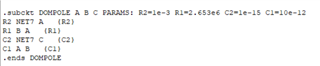

在互阻抗设计中、环路相位裕度主要受模型中主极点位置以及源极 C 和反馈 C 的影响。在模型中、主极点非常简单、 正向路径中的高阶极点和传播延迟对于低电压增益应用而言并不重要、而是变得更加重要。这里是主极点模型中的区域、将 C1更改为在电路中测试器件。 此外、我认为我在本文中使用 ZT 设计来说明相补角测试、是的、最后我参加了有关 LG 相补角的 ZT 设计讨论。 36度通常适用于 ZT 设计、但您不应振荡-在生产中、您需要解决该问题、而不应忽略它。