https://e2e.ti.com/support/amplifiers-group/amplifiers/f/amplifiers-forum/1048202/tlv4041-tlv4041

器件型号:TLV4041您好!

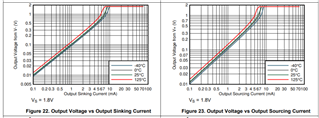

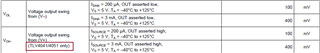

我正在设计 TLV4041R5DBVR 推挽式器件(我更喜欢漏极开路、但遗憾 的是、封装中没有比微型 DSBGA 更大的漏极开路器件)。 我需要将该比较器的输出连接到 FPGA 的 LVCMOS18输入(比较器和 FPGA 组都使用1.8V 电源)。 数据表中该比较器的 VOL/VOH 的唯一相关信息是:

我无法控制 IsSource (顺便说一下它是什么?)、并且 Vs=1.8V。 我觉得 FPGA 引脚可以切换、因为 FPGA 的 VILmax=0.63V、VIHmin=1.17V、但如何在这里为 VOL/VOH 提供正确的数字? FPGA 引脚泄漏电流<|15|uA。