欢迎 TI 工程师! 我将 OPA699用于扫描电路、并目睹了一些意外失真。 以下是事实:

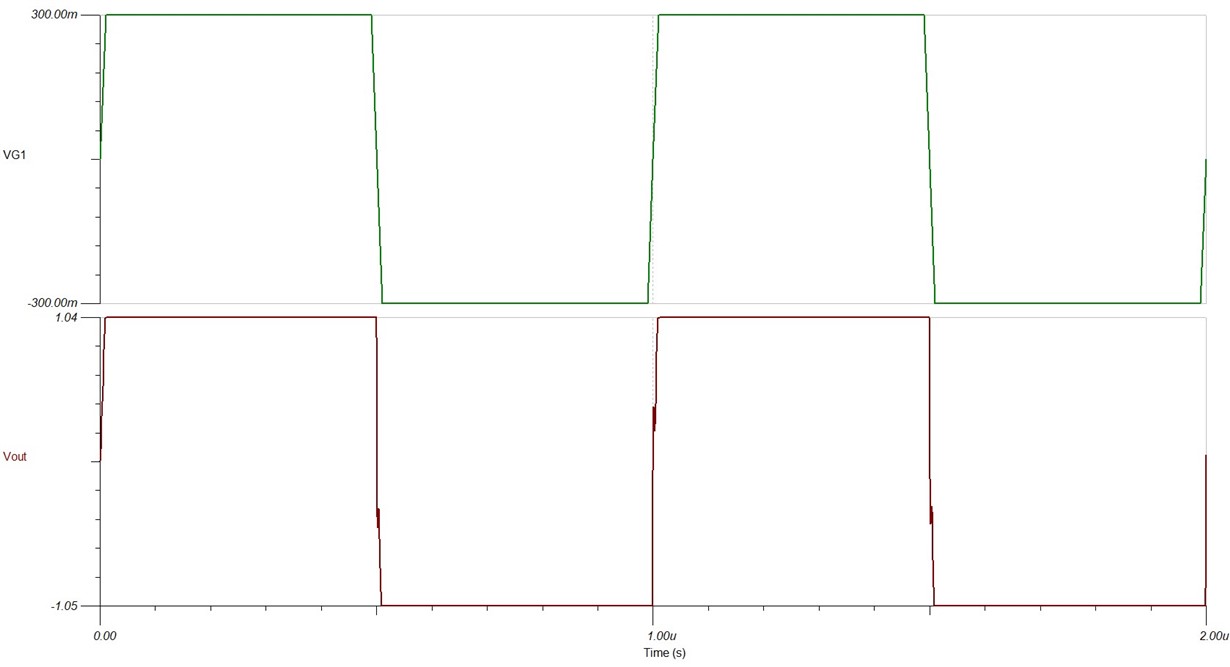

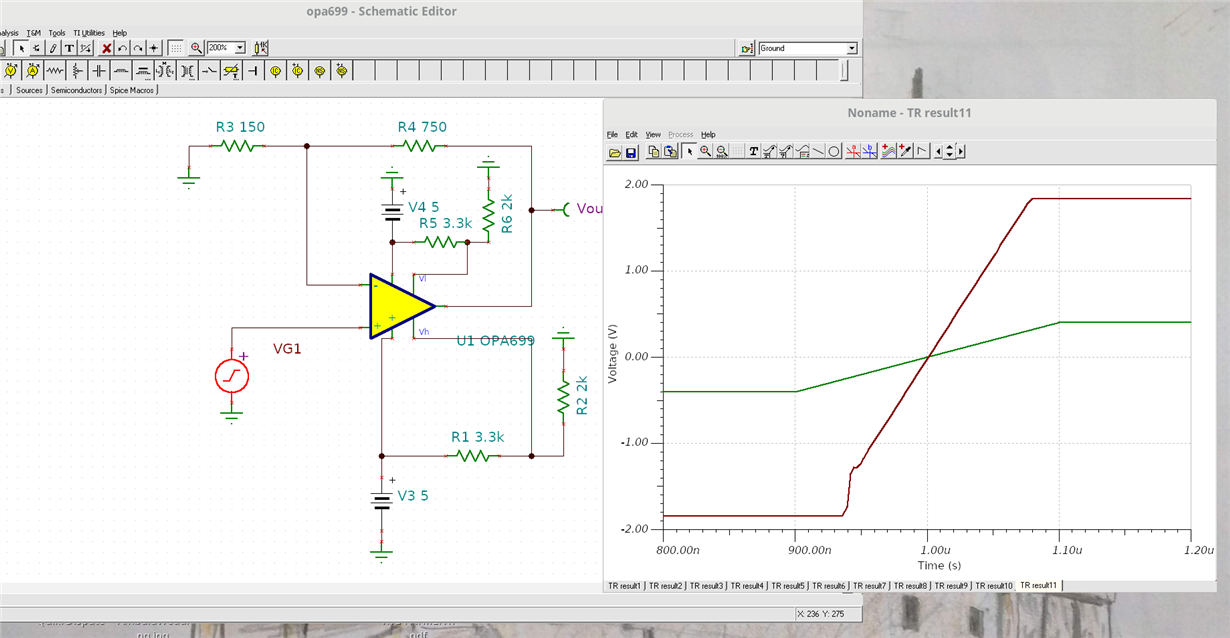

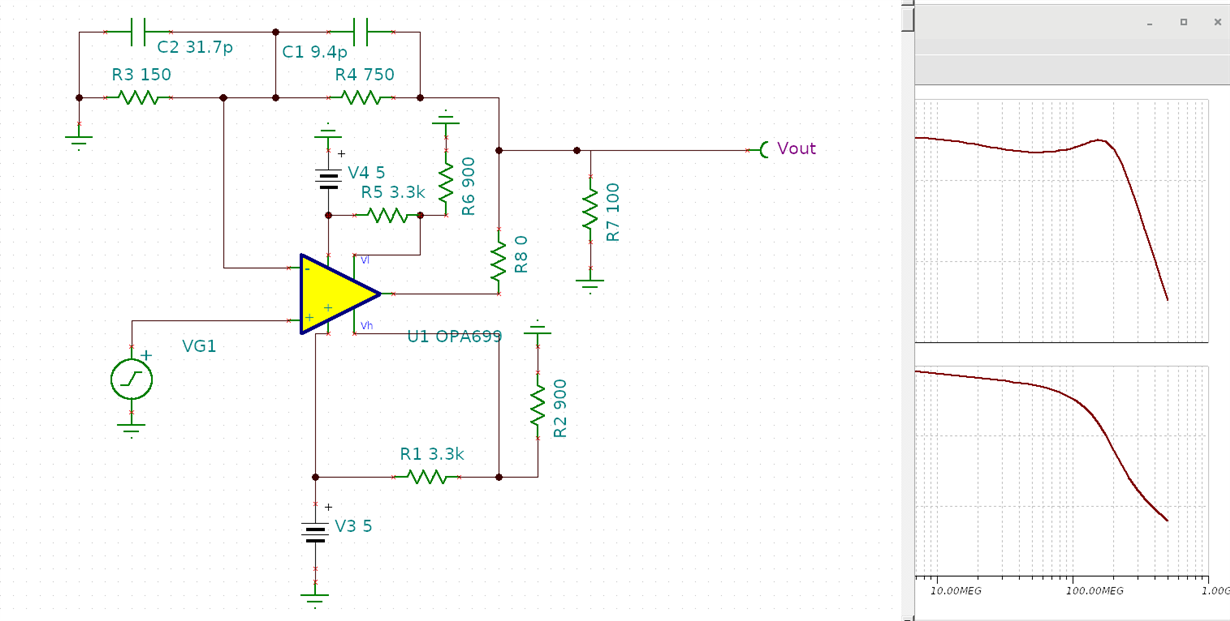

双电源=+/- 5V。 G =+6、RF = 750欧姆。 无电容器。 OPAMP 和 LIMIT 引脚被0.1uF 旁路掉

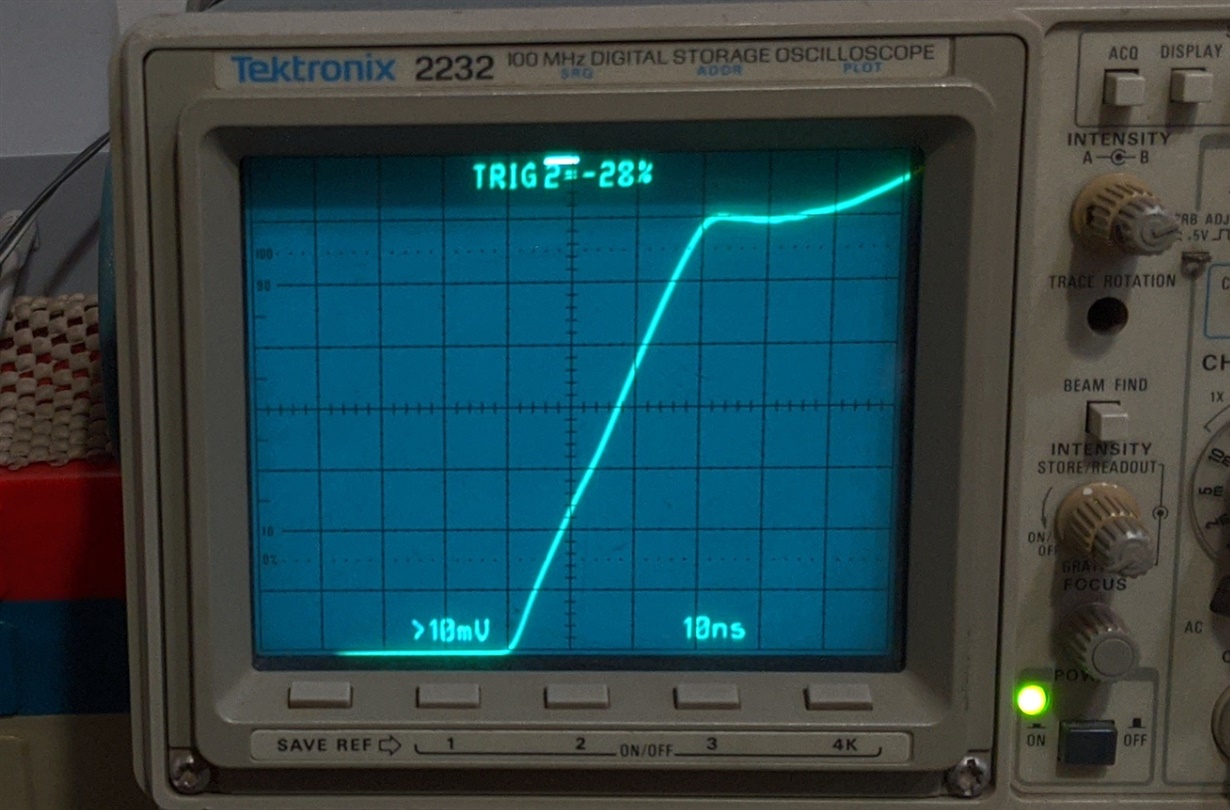

2.由另一个运算放大器馈送的同相输入、在50V/us 下生成-0.3V ->+0.3V 斜坡、总信号峰值几乎为+/- 0.6V。

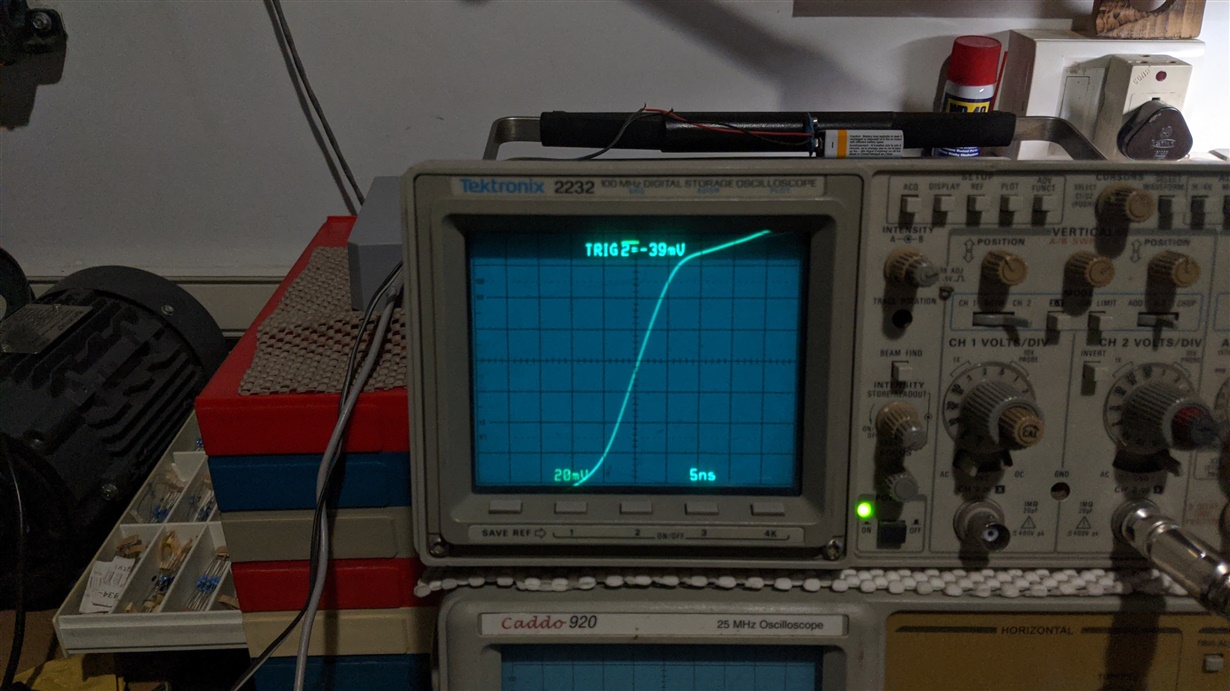

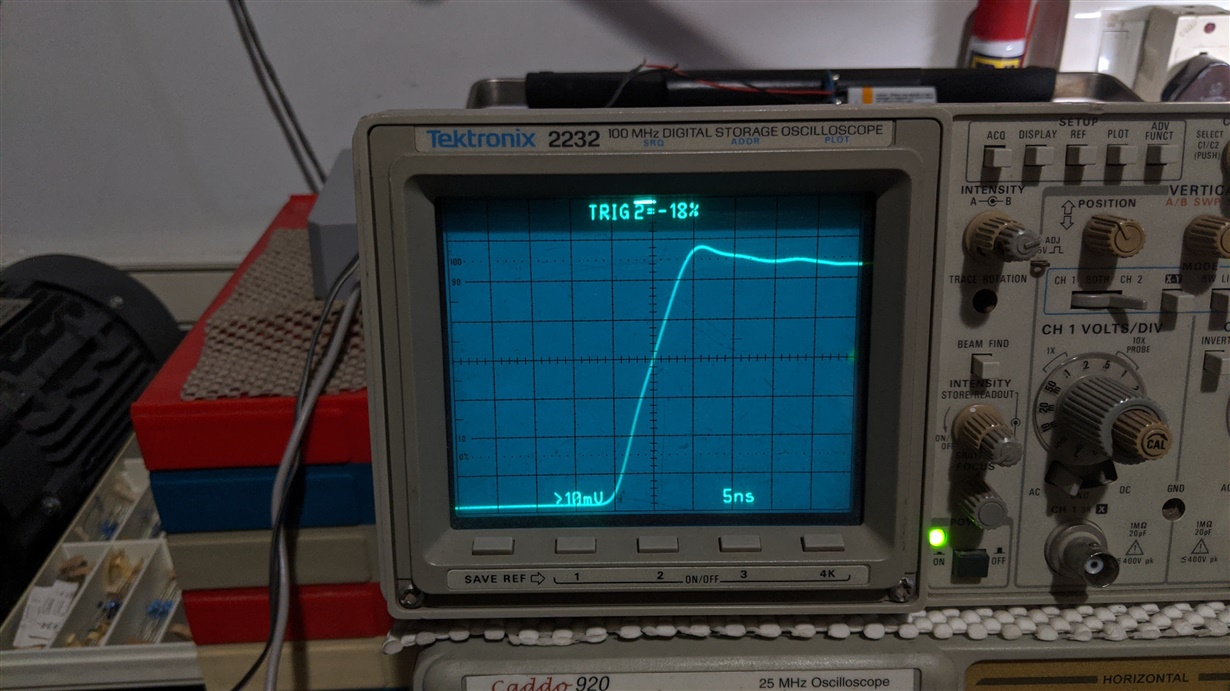

3.在限制引脚断开的情况下,我在输出端得到了一个看起来如预期的斜升。 但是、当限值设置为+/- 2V (或更低)时、我会得到明显失真的斜坡。 不是"严重"、而是"明显"。

我感到困惑、因为似乎我没有以太快的输入斜坡推动放大器。 有什么建议吗? 放大后的信号峰值(G=+6X0.6V = 3.6V)是否超出3.2V 的输入电压范围会导致问题?

提前感谢。

最佳- RAM