https://e2e.ti.com/support/amplifiers-group/amplifiers/f/amplifiers-forum/909870/tlv4112-oscillating

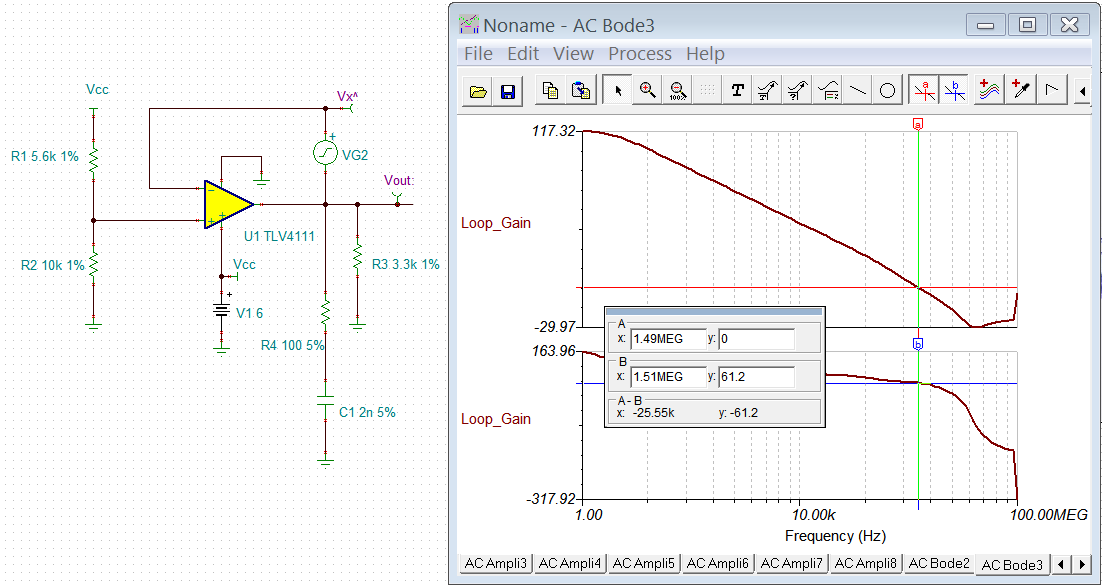

器件型号:TLV4112主题中讨论的其他器件:TLV2772、 TLV4111、 TINA-TI、 LM7332、 UA741

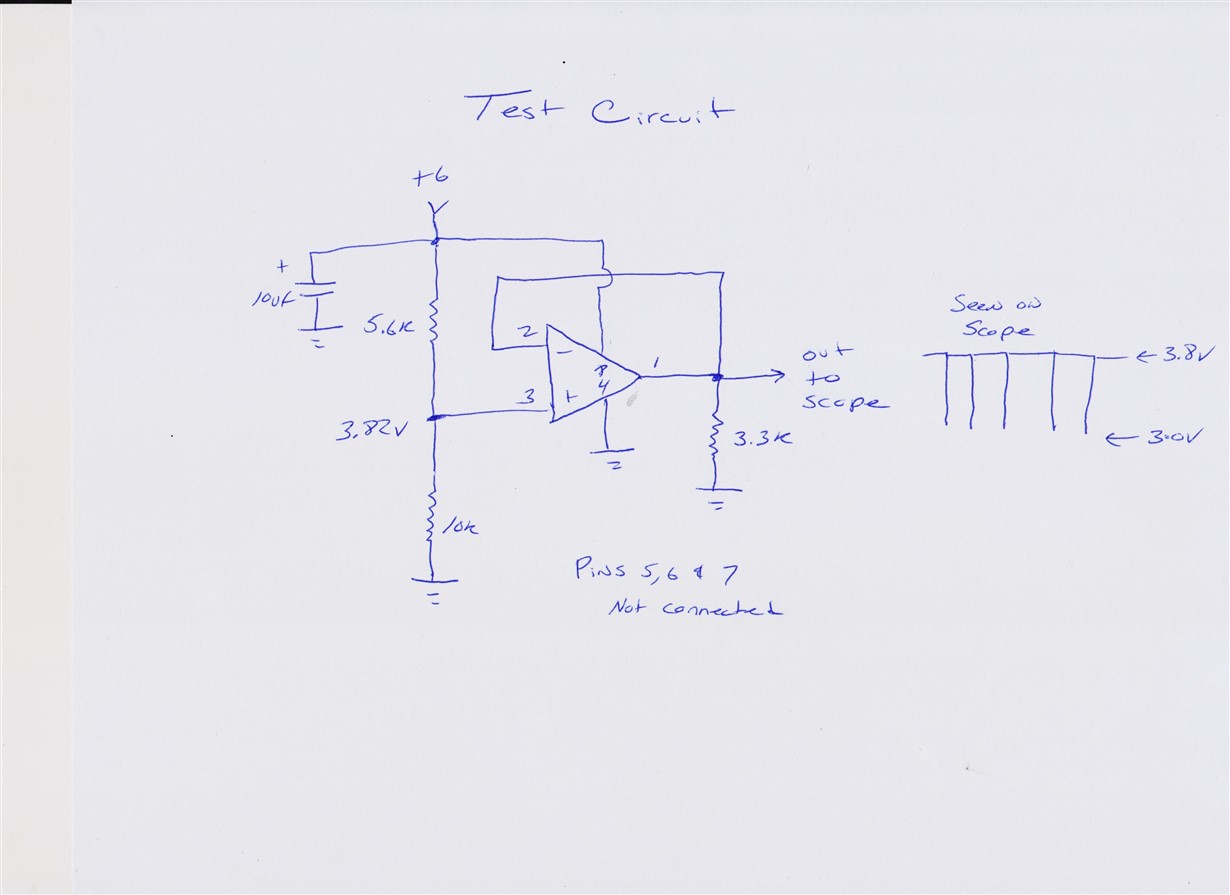

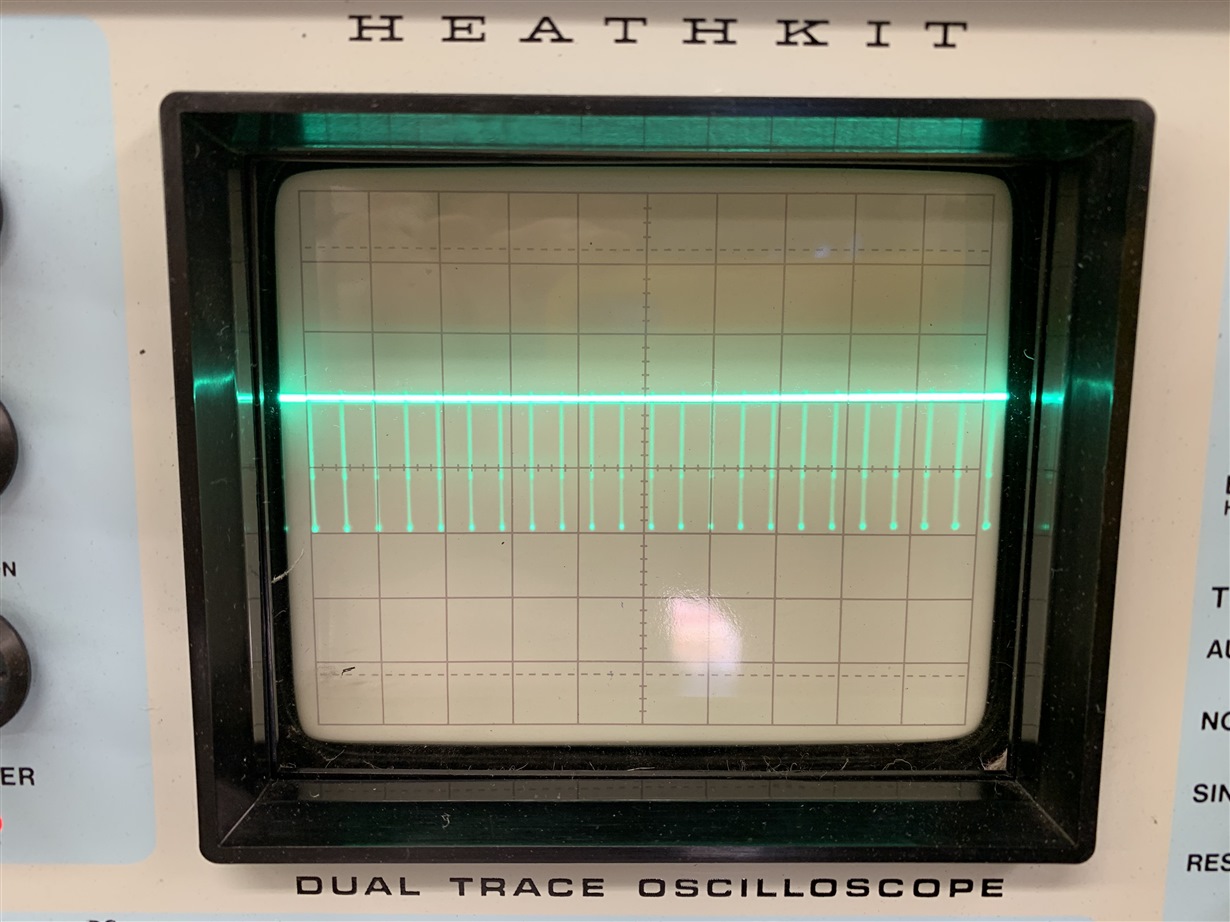

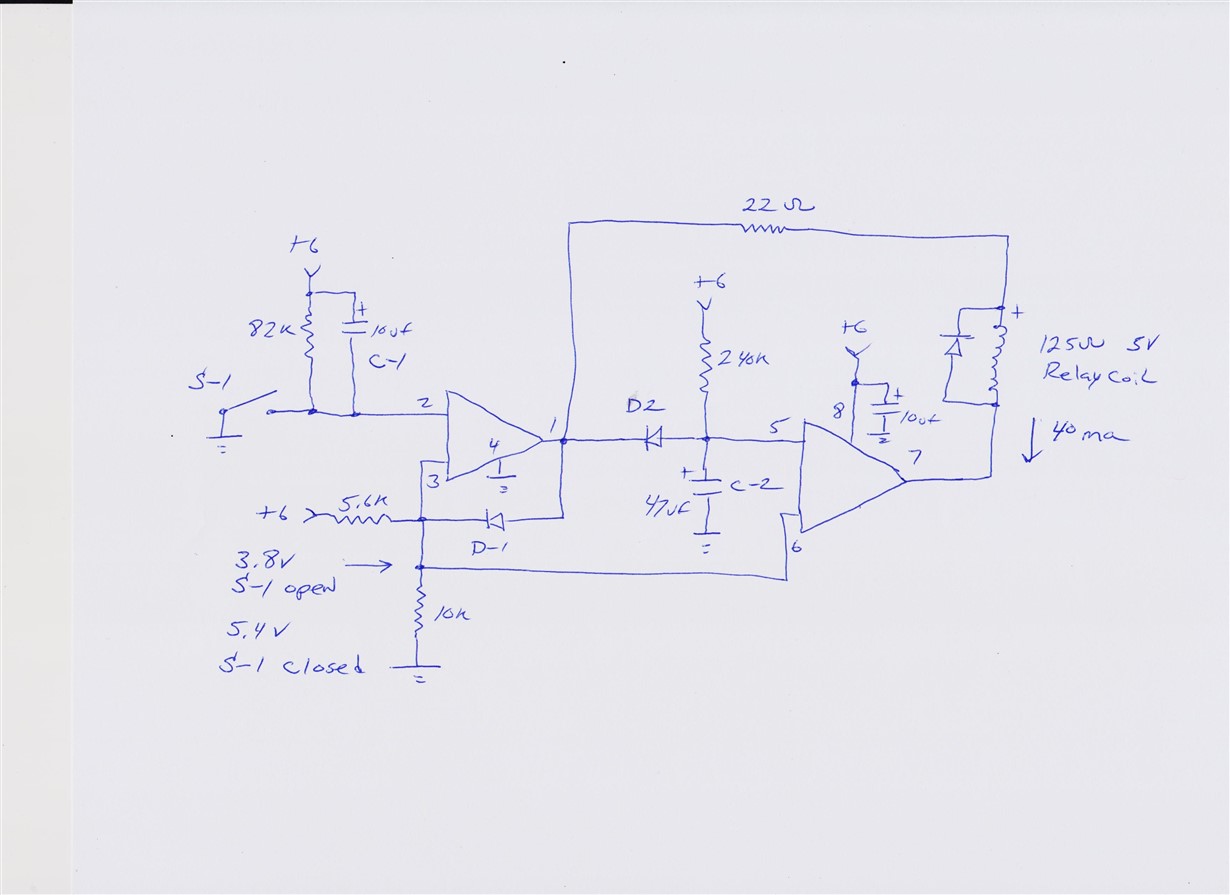

由于 TLV2772CP 无法驱动我的负载、因此为新设计购买了其中的2个 TLV4112CP。 只要 负载不重、我的设计就可以在 TLV2772上正常工作、尽管我从未在 TLV2772上看到过任何振荡。 因此、当我在电路中放置 TLV4112CP 时、它会振荡。 为了尝试确定它的来源、 我 对电路进行了调整、并构建了一个测试电路 作为电压跟随器。 我在 +输入端施加3.8伏电压、在输出端产生一系列脉冲(振荡)。 我从未见 过增益为1的运算放大器振荡。 电源 为6V 单电源 、在 整个芯片上具有10uF 旁路。 在我看来、问题是芯片内部的设计问题。 您能给它下些光吗?