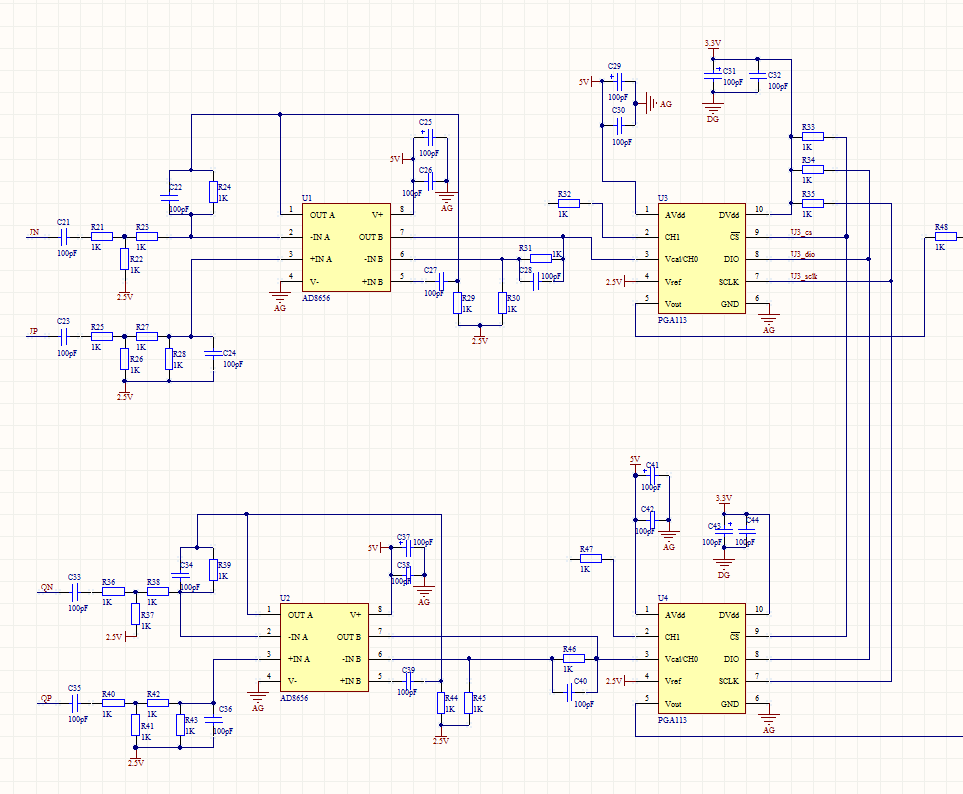

PGA113的 CLK、CS 和 DIO 时序图正确、相关引脚连接正常、但 pga113无法放大。 输入0x2a50的默认放大倍数为1。 我不知道原因?

#define PGA_SET_SCL () GPIO_SetBits (GPIOI、GPIO_PIN_2)// PI2->U3_SCLK

#define PGA_CLR_SCL () GPIO_ResetBits (GPIOI、GPIO_PIN_2)

#define PGA_SET_CS () GPIO_SetBits (GPIOI、GPIO_PIN_0)// PI0->U3

#define PGA_CLR_CS () GPIO_ResetBits (GPIOI、GPIO_PIN_0)

#define PGA_SET_DIO () GPIO_SetBits (GPIOI、GPIO_PIN_1)// PI1->U3_DIO

#define PGA_CLR_DIO () GPIO_ResetBits (GPIOI、GPIO_PIN_1)

void PGA113_Write (U16 ads_dat)//mode 1.1

{

unsigned char i;

PGA_SET_CS ();

PGA_SET_SCL ();

PGA_CLR_CS ();

延迟(0x100);

PGA_CLR_SCL ();

延迟(0x100);

对于(i = 0;i < 16;i++)

{

PGA_SET_SCL ();

if (ads_dat&0x8000)

PGA_SET_DIO ();

其他

PGA_CLR_DIO ();

延迟(0x100);

PGA_CLR_SCL ();

ads_dat <<= 1;

延迟(0x100);

}

PGA_SET_SCL ();

延迟(0x100);

PGA_SET_CS ();

}

int main (空)

{

PGA113_Initiate();

while (1)

{

PGA113_Write (0x2A40);//0x0010 1010 0100 0000

}

}

黄色是 SCLK、蓝色是 DIO、输出波形无法放大、为什么?