请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:INA226-Q1 您好、Supoort 团队

请帮助检查 INA226-Q1以了解低侧和高侧原理图:

低侧:关于 VBUS 连接是否正确? Isense 电阻可能会像数据表中所示更改为2欧姆?

高侧原理图:

如有任何建议、请告知我。

谢谢、

此致、

劳伦斯

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

大家好、Lawrence、

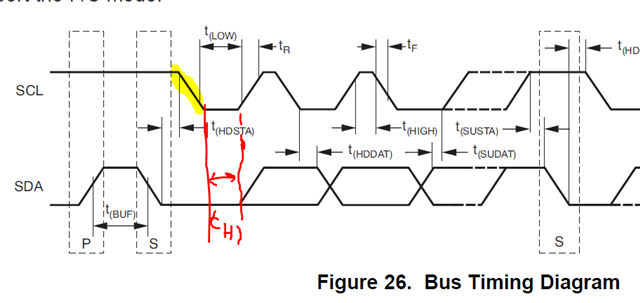

原理图看起来不错。 我应该注意的唯一一点是、您应该尝试将第一个 SCL 下降沿(下面时序图中的 t_H1)之后的最小数据保持时间增加一个额外的100ns。 当将地址引脚设置为 SDA 时、这是一个特定的要求。 原因是器件测量第一个 SCL 下降沿的地址引脚以确定其自身的二次地址。 如果 SDA 在 SCL 下降时右移高电平(突出显示的部分、因此 t_h1=0)、则器件将无法正确确定其地址。 因此、请确保 t_H1 >(10ns +100ns)。

此致、

Peter