Other Parts Discussed in Thread: TLV3601, TLV3602, TINA-TI

主题中讨论的其他器件: TLV3602、 TINA-TI

您好!

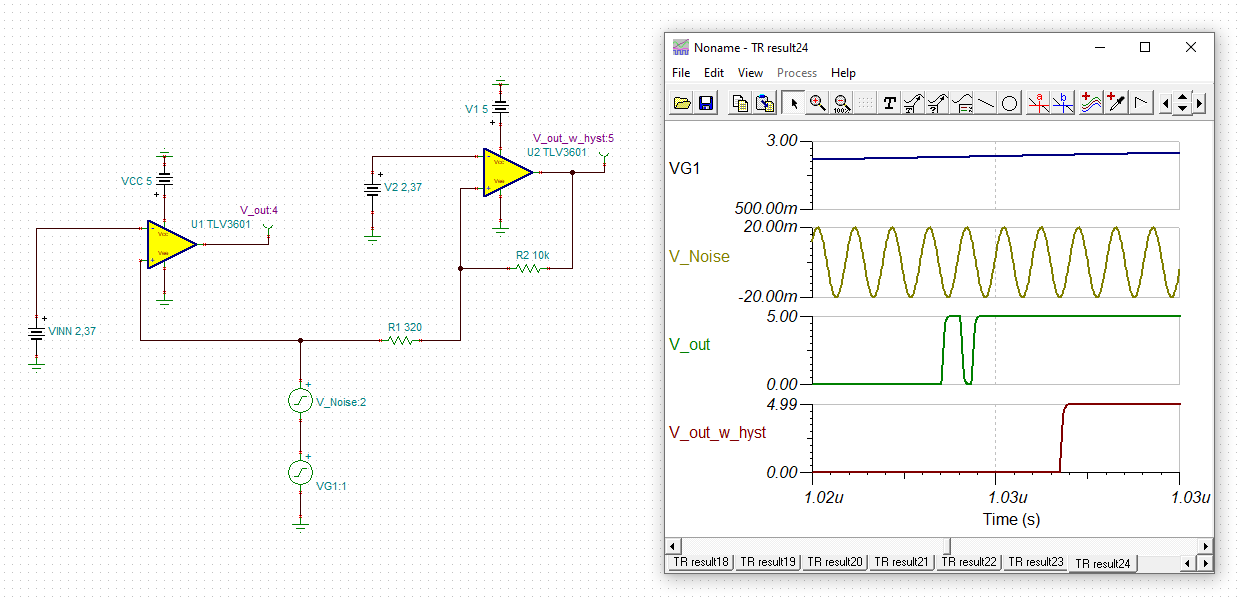

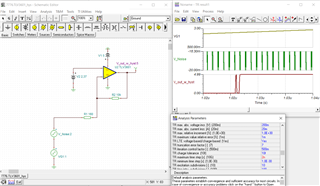

我希望在 TLV3601或 TLV3602的同相配置中使用外部迟滞。 我的迟滞电压(V_hys)为80mV。 迟滞电阻根据 TLV3601数据表中的公式(3)进行计算。

![]()

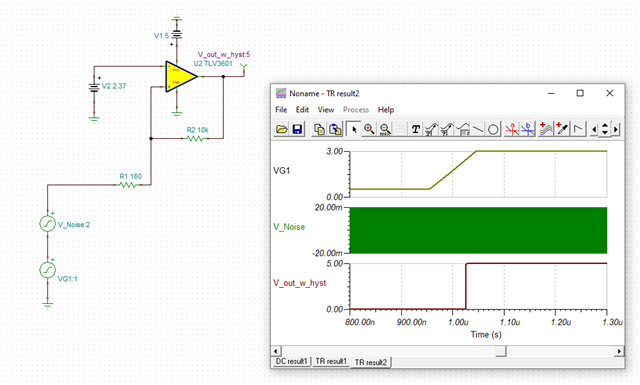

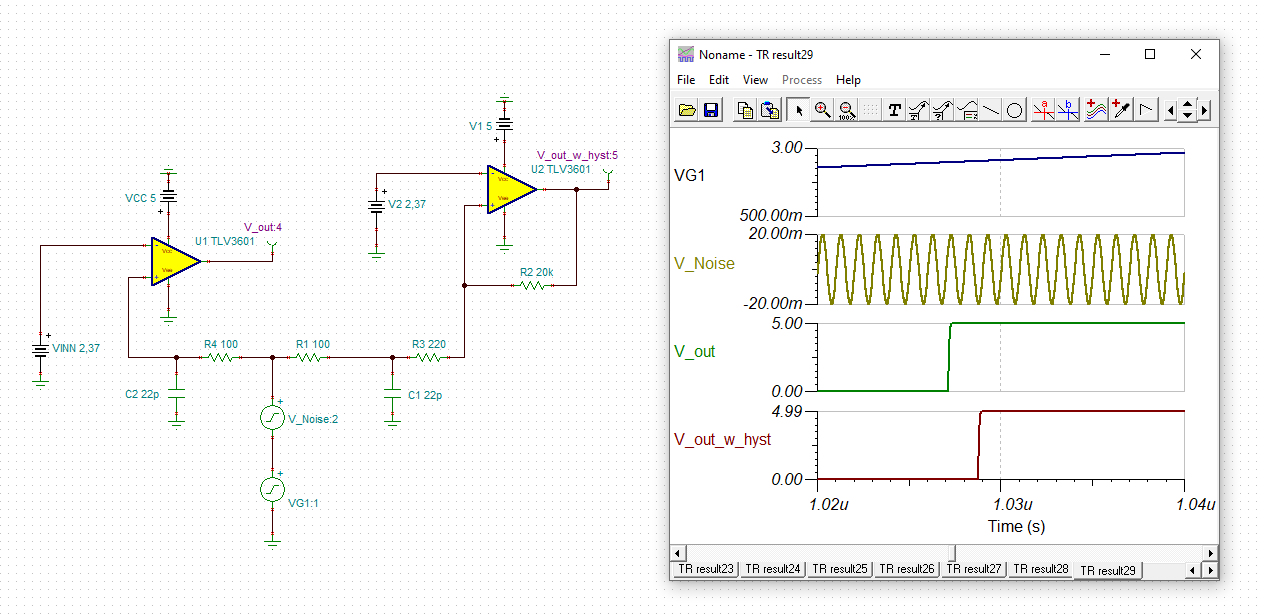

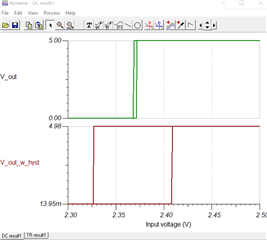

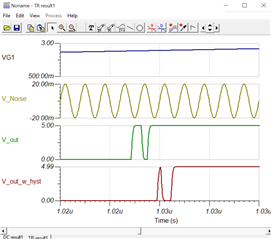

在下面、您可以找到 我的仿真电路的 Tina-TI 文件。 虽然 TINA-TI 中的直流传输特性表明 V_hys = 80mV、但在峰峰值噪声电压为40mV 的瞬态分析中、磁滞电路不起作用。

这样做的原因可能是什么?

此致、

Kara