Other Parts Discussed in Thread: REF3333, INA240

主题中讨论的其他器件:REF3333、

尊敬的 TI E2E 团队:

感谢您管理良好的论坛和支持。

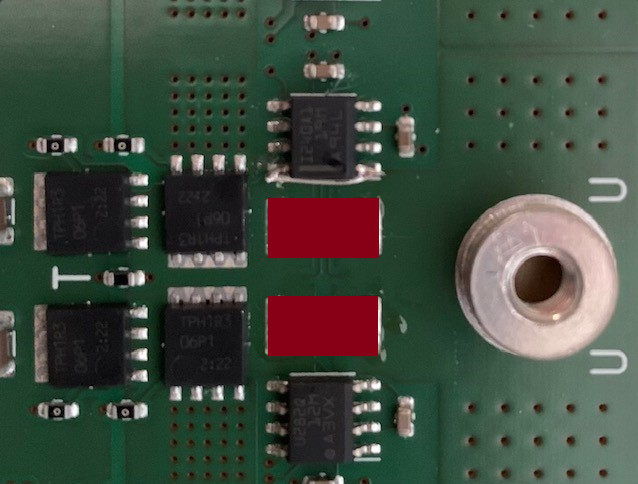

目前 、PMSM 电机驱动板的电流感应电路存在问题。

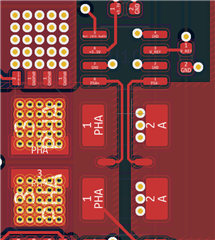

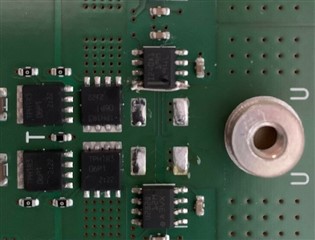

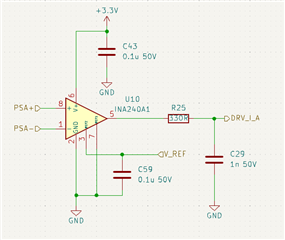

我们使用 三个 INA240A1内联感测相电流:

PSA+和 PSA-是 Kevlin 连接到分流电阻器、而 DRV_I_A 信号连接到 ADC 输入。 V_REF 输入直接取自 REF3333电压基准。

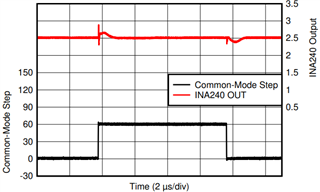

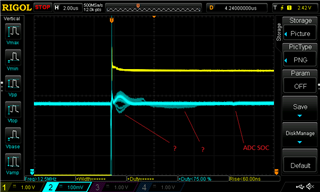

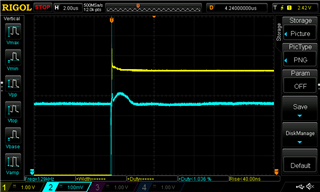

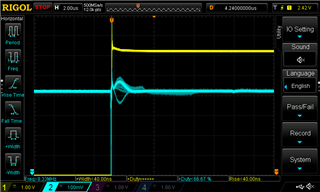

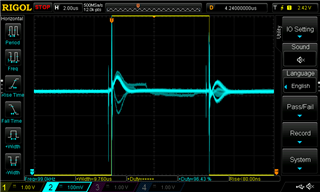

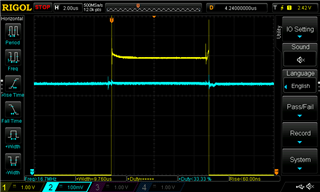

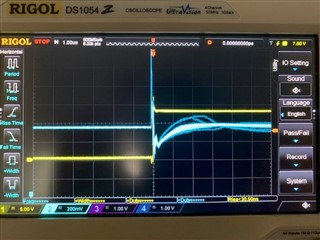

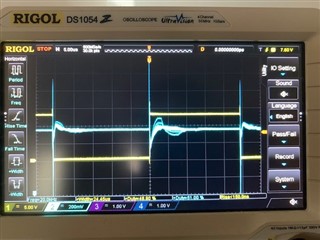

以50%占空比和空载驱动电机相位时、我们看到 INA240输出意外运行: 有时会出现完全不同的信号波形:

通道1、黄色:PSA-/相位输出

通道2、蓝色:DRV_I_A / INA240输出

较长的稳定时间和奇怪的波形使得我们的 ADC 读数无法使用。 我们在这里经历了什么?

感谢您的支持。

本