主题中讨论的其他器件: OPA818

您好!

我要测试中所述的设计

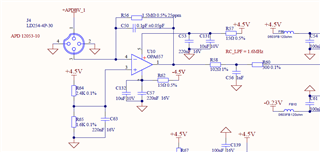

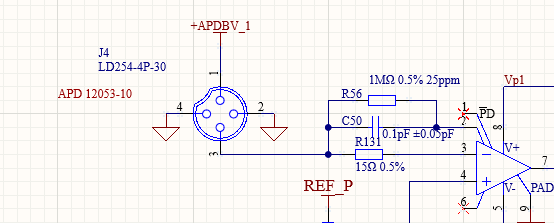

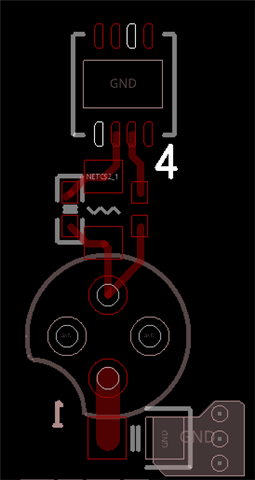

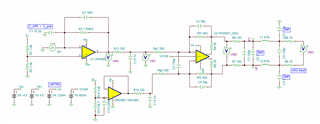

最终电路图如下:

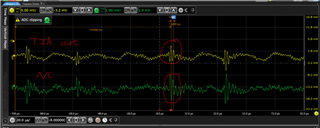

而且 OP657的输出噪声很大。 最大 值约为40mVp-p (我使用了一根轴向电缆和100Ω Ω 隔离电阻器,波形与 ADC 输出的结果相同,因此是可信的)

我已确认所有电源、纹波/噪声均低于3-5mV。

然后、我移除了反馈电容器、但仍然保持不变。

然后我将增益电阻器更改为1k 和100k、结果如下:

1k - 0.5mVpp 相当好;

100k - 1.47mVpp

400k - 9.6mVpp

似乎在 OPA657的输入端上有一些电流噪声并进行放大。

我对环境有所怀疑、因此我还有 另一个 示波器通道 、使用相同的轴向电缆、除了靠近 PCBA (以下波形中为 NC)之外什么都没有连接。

我想这些尖峰来自环境。

但是降低尖峰、 TIA 的输出上似乎有一个正弦波形。

我进行了相位裕度仿真、并尝试了不同的反馈电容器、但结果无效。

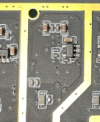

有痕没有卖面具安装钢屏蔽壳,但我仍在等待交付.

在获得镀层零件之前、我还能尝试其他什么?

谢谢!

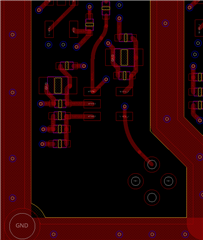

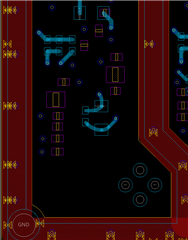

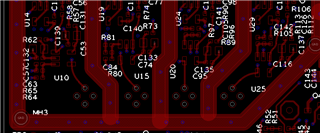

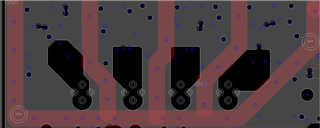

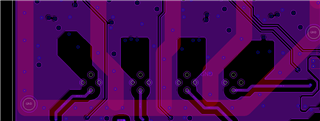

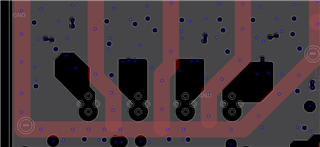

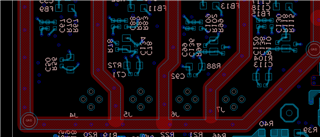

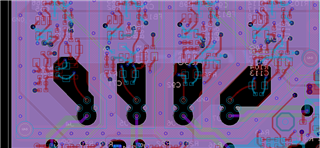

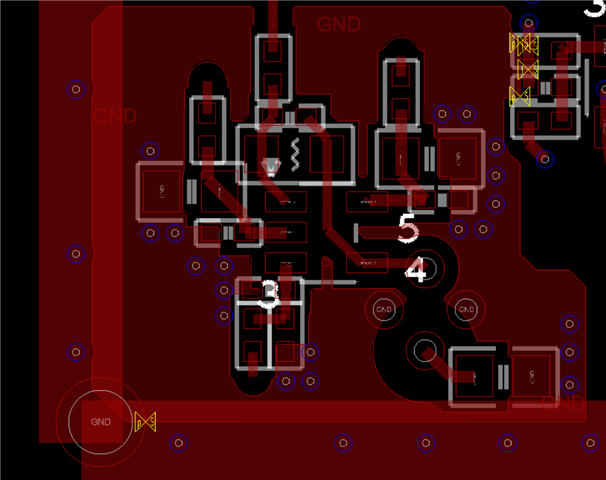

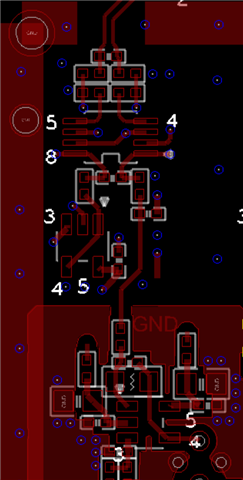

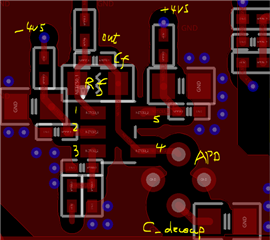

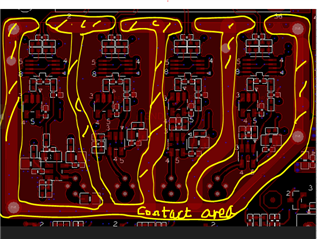

布局: