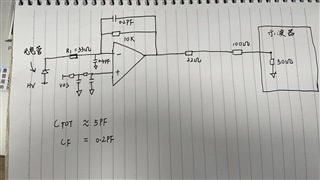

我们的客户在 TIA 电路中使用 OPA855。 以下是它们的测试环境、 TIA 的右侧是示波器、另一个是光电二极管。

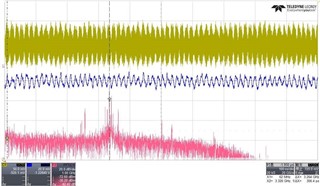

但存在高频振荡。 下面是波形、黄色是 TIA 输出、粉色是 FFT 频域波形。 如波形所示、100MHz 包络信号存在3.3GHz 噪声。 客户更改了电容、但没有影响。

它们应该怎么做来降低噪声? 希望您能为他们提供一些方法来避免这种情况。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

尊敬的 Minghao:

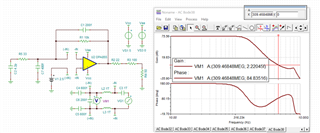

经过对电路的稳定性分析后、大家分享了、看来电路是稳定的。 我确实根据您提供的值进行了一些假设、但总的来说、我仿真的电路的表示看起来是稳定的。 电路连接在下面。

e2e.ti.com/.../4454.OPA855_5F00_stability.TSC

有了这些信息、我确实有几个问题。

此电路是否有可用的 PCB 布局? 原因是、可能会根据电路板的布局而引入额外的寄生效应。 这可能导致电路变得不稳定。

使用33欧姆电阻是否有原因? 这会对光电二极管建模吗? 这可能会导致电流到电压转换过程中产生一些混乱、并导致意外结果。

我还想指出、具有电流负载的电路与示波器不匹配、这可能会由于这种不匹配而导致意外结果。 我们建议匹配仪器的输入阻抗、以限制可能发生的任何反射。

此致、

伊格纳西奥

尊敬的 Minghao:

没错、当运算放大器电路振荡电路的相位裕度不足以满足要求。 在这种振荡状态下、电路不稳定并在某种不可预测的频率下振荡、这可能是3.5GHz 信号所看到的情况。 电路配置就是导致两个输入上的信号之间出现这个相移的原因。如果存在足够相位差、这就是在电路变得不稳定并导致振荡的时候。 然而、从我之前分享的分析来看、使用共享的元件值来看、电路似乎是稳定的。

PCB 的设计还会由于不必要的寄生效应而影响电路的相位裕度、这可能是出现稳定性问题的原因。 虽然并不常见、但我们也看到了由于电源电压滤波不当而产生的振荡。 由于 电源滤波不良、PCB 布局不太理想、这一组合导致放大器输出端出现振荡型行为。

此致、

伊格纳西奥

尊敬的 Minghao:

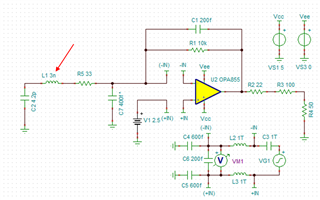

该团队能够深入研究您在较高频率下看到的现象、 我们倾向于认为这可能是由光电二极管的非理想特性导致的。 通过假设键合线 电感等非理想特性(可以粗略估计)、我们能够看到最初 测量的3.3GHz 附近的峰值。

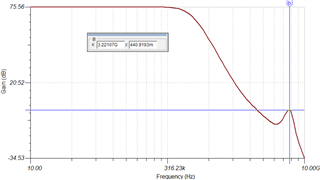

这种非理想性 可以建模为与 二极管电容串联的电感器、如下图所示。 运行稳定性仿真可显示所测量范围内的峰值。 理论依据如下:额外的 电感会隔离 二极管 电容、并且会在较高频率下整形噪声增益。

e2e.ti.com/.../2642.OPA855_5F00_stability.TSC

e2e.ti.com/.../2642.OPA855_5F00_stability.TSC

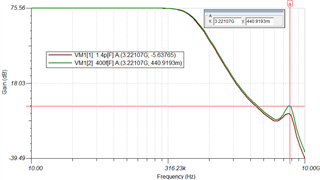

有人建议 应对这种情况、在反相节点接地时添加更多电容。 下面是一个仿真、该仿真对具有 400fF 原始输入电容(绿色迹 线)和一个增加电容为1.4pF (栗色迹线)的电路进行了仿真。 结果在那些较高的频率上显示出较少的峰值。

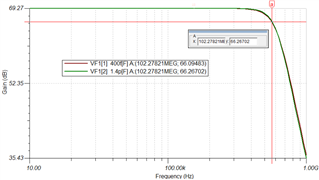

我们还运行了闭环带宽仿真、结果表明增加的电容 不应影响系统的带宽。

e2e.ti.com/.../OPA855_5F00_BW.TSC

e2e.ti.com/.../OPA855_5F00_BW.TSC

如前所述、APD 中的非理想因素似乎是导致您遇到此问题的原因、但类似的非理想寄生效应也是由于 PCB 布局未应用最佳实践而产生的。

此致、

伊格纳西奥

尊敬的 Minghao:

是否有方法可以向电路板添加额外的输入电容以测试这是否有助于其振荡问题、这将缩小 PCB 布局可能导致一些不稳定的范围。 您还能否提供他们为了获得相位裕度而进行的分析?

至于闭环输出阻抗问题、我可以进一步看一下、由于闭环输出阻抗取决于几个因素、因此在较高频率下是否有任何额外数据。

您看到+7V/V 和-7V/V 之间差异的原因是放大器配置了不同的配置。 虽然它们都具有7V/V 的信号增益幅度、但这两种配置的噪声增益是不同的。 尽管两种信号增益幅度都为7V/V、但该配置差异仍会导致数据表中看到的性能变化。

此致、

伊格纳西奥