Other Parts Discussed in Thread: OPA2210, OPA211

主题中讨论的其他器件: OPA211

大家好!

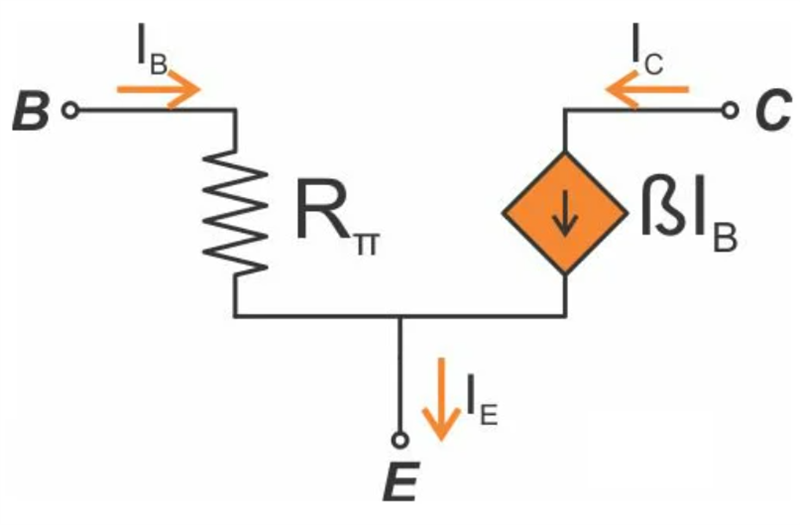

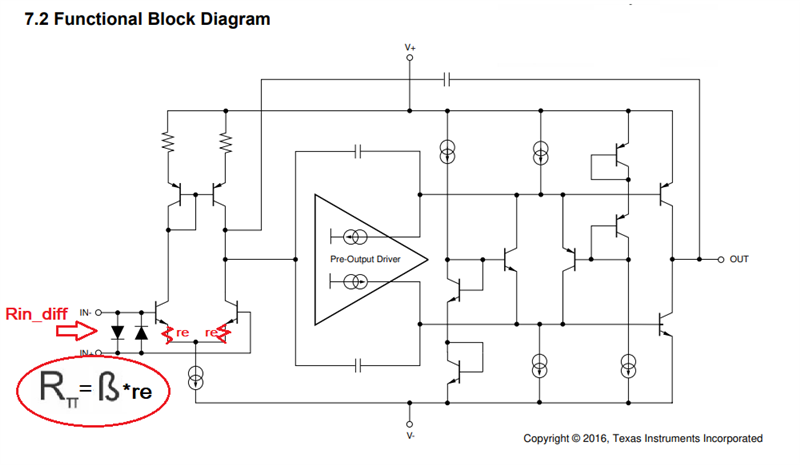

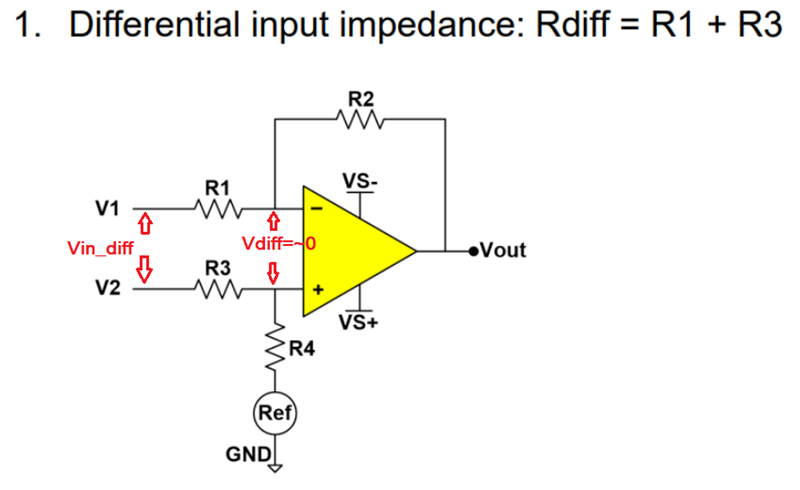

我的客户正在使用 OPA2210进行电压监控、该配置为具有前期电阻分压器的差动放大器、他们有这个问题:

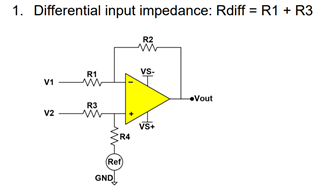

在数据表中、他们查找差分输入阻抗:

但请怀疑400kOhm 的阻值是否正确、因为它看起来非常低。

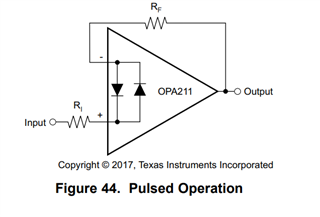

在 PSPICE 模型中、他们可以找到:

R_DIFF ESDN ESDP 无噪声100MEG

他们的评论是,即使这看起来相当低。

您能否对应该期望的差分输入阻抗值进行评论?

此致

乌埃利