主题中讨论的其他器件: OPA2196、OPA192、 TINA-TI、 ADS7046、 ADS8860、OPA320、 OPA328、 OPA625

您好!

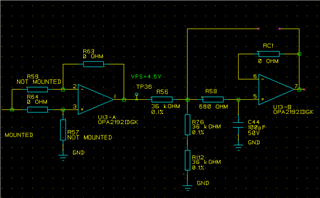

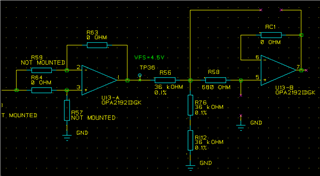

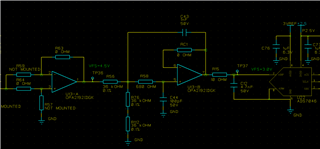

我们采用上述运算放大器配置来测量海上应用(800kW 至6MW 功率范围)变频器中的直流链路电压。 (该电路前面没有显示高压分压器)。 运算放大器由单电源轨(GND 至+15V)供电。 我们需要能够测量接近0V 的电压。 我选择了 OPA2192、因为它具有"超出电源轨"的性能。 (由于传统原因、存在分压器 R56+R76+R112、我们在之前的设计中采用了5V ADC)。 当我用0V 输入馈送该电路时、在 U13-A 放大器(缓冲器)的输出端测得0.6mV。 在 U13-B 放大器(滤波器)的输出端、我得到19.3mV。 这远远超出了我的预期。 如果我移除电容器 C43和 C44、则在 U13-B 的输出端得到3.1mV 电压。 这更符合我的预期。 进入 U13-B.5的输入偏置电流应为5-20pA。 在20pA 和36k|||72k=24k 阻抗下,它应该是0.48uV (?) 为什么在没有电容器的情况下偏置电流更少?

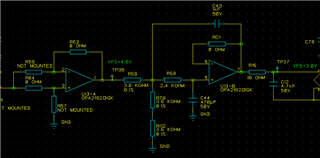

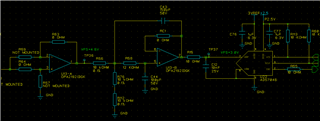

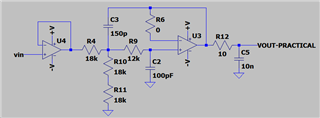

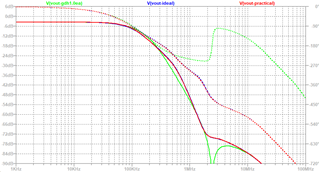

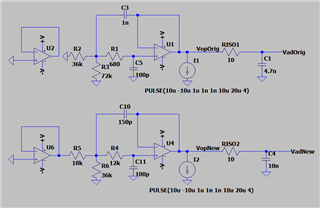

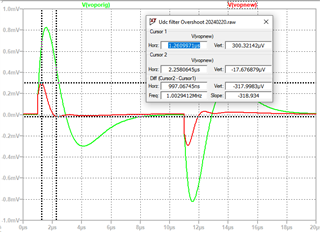

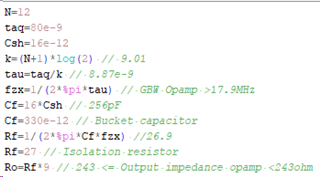

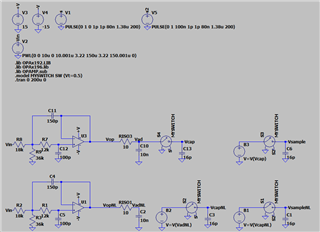

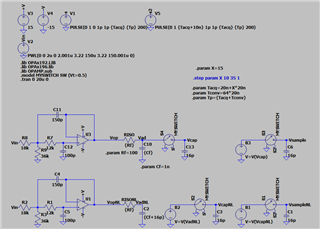

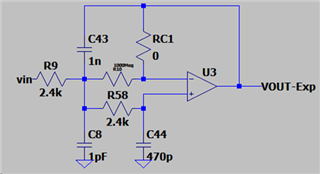

作为一个实验、我重新设计了滤波器级以降低电阻、如下所示:

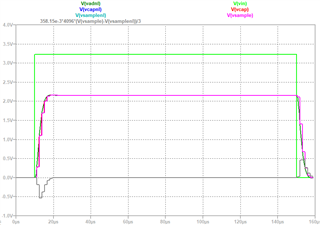

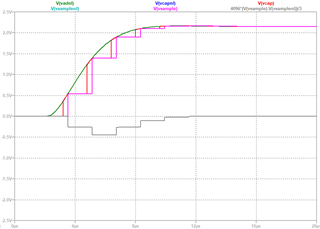

结果我在缓冲器级输出上得到0.8mV、在滤波器级输出上得到5.9mV (成功)。

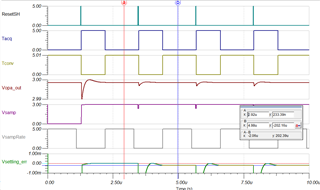

对于我的电路和0V 输入电压、滤波放大器的偏置电流似乎是这样的:

原始电路:(19.3mV-0.6mV)/(24k Ω+680 Ω)=0.76uA

经修改的(较低电阻)电路:(5.9mV-0.8mV)/4.8k Ω=1.062uA

我看到您在数据表的图18中有一个输入偏置电流与共模电压间的关系图。 该图仅显示共模范围的中间值。

输入偏置电流如何在接近负电源轨时发生变化?

(PS:根据可用性和成本、我们可能会更改设计以使用 OPA2196。 我也能获得该器件的类似结果)