主题中讨论的其他器件: TPSI3050-Q1、 OPA2991、 LM2904B-Q1、 OPA310、OPA991、 TPSI3050、 CSD19534Q5A、 CSD19538Q2

您好!

我正在开发一个模拟电压测量0。 10V、除了其他外、要求输入阻抗介于850k Ω 和900k Ω 之间(对于电压范围0V-10V)。

这位于 功能强大且功率更高 状态!

对于供电状态、OPA2991-Q1非常适合(低输入泄漏电流)。

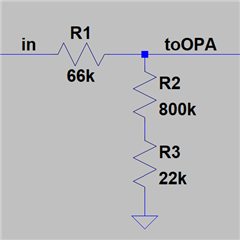

输入分频器如下所示。 该系数应该接近1、以引入电阻引起的最小误差(已选择0%、1%)

但在未加电状态下、连接到正电源轨的内部保护二极管(在该情况下为 GND 电位)将导通并"缩短"R2和 R3。

我已经尝试通过 FET (由 TPSI3050-Q1驱动)来"打开"与 OPA 的连接。 这会有所帮助、但 FET 漏极-源极泄漏电流也会通过内部保护二极管产生相同的问题。

我的问题:

- 是否有具有"绝对"输入电压能力的 OPA?

高达10V 就足够了。 性能应与 OPA2991类似(双极电源、低输入泄漏电流...) - 如果没有这样的 OPA;是否有具有极低漏源漏电流(<10nA)的 FET

谢谢!

塞巴斯

蒂安