Other Parts Discussed in Thread: OPA564

您好!

我正在使用 Vanalog =+/-5、5V 的 OPA564。

我在数据表中读出(V-)+ 3.0V≤VDIG≤(V–)+ 5.5V

因此我知道我的 Vdig 必须在-2.5V 和0V 之间、因此必须为负。

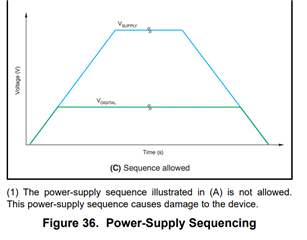

但我无法理解如何实现数据表图36中所述的上电序列。 这是否意味着我必须从-5V5开始 Vdig 序列?

此外、Vdig 为负是否意味着所有标志也将为负?

谢谢。

西尔万

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Other Parts Discussed in Thread: OPA564

您好!

我正在使用 Vanalog =+/-5、5V 的 OPA564。

我在数据表中读出(V-)+ 3.0V≤VDIG≤(V–)+ 5.5V

因此我知道我的 Vdig 必须在-2.5V 和0V 之间、因此必须为负。

但我无法理解如何实现数据表图36中所述的上电序列。 这是否意味着我必须从-5V5开始 Vdig 序列?

此外、Vdig 为负是否意味着所有标志也将为负?

谢谢。

西尔万

尊敬的 Sylvain:

正确的做法是、VDIG 电源必须介于3.3V 和5.5V 之间、以 V-为基准。 这意味着、当您的 V-=-5.5V 时、VDIG 可在0V 下工作。

对于如图36所示的电源时序、假设 Vsupply =(V+ −V-)和 Vdigital =(V-+ VDIG)、其中 VDIG 为数字电源引脚上的电压(引脚7或14、取决于封装)。

考虑图36中的序列 C。 假设关断状态下的 V+等于0V、您只需在斜升 V+电压之前、对 V-电源斜升至5.5V 的时序。 在这种情况下、Vdigital 和 Vsupply 以相同的速率斜升、Vsupply 在 Vdigital 被设定为其正确值之前不会超过 Vdigital。

标志输出也以 V-和 VDIG 为基准。

此致、

扎赫

尊敬的 Sylvain:

在这种情况下、VDIG 可以直接接地(0V)。 无需在 VDIG 引脚处设置正电压。 我仿真了下面的一个示例电源序列。

请参阅 VDIG 引脚始终接地、但数字电源电压(Vdigital)以 V-为基准。 我注意到、我给出了不正确的 Vdigital 公式、它应该被定义为 Vdigital =(Vdig - V−)、这样、当 Vdig = 0V、V−=-5.5V 时、Vdigital =+5.5V。

在仿真中、 V−变为-5.5V、然后 V+变为+5.5V。 在断电时、V+必须斜降至0V、然后 V−可以斜升至0V。 在这种情况下、在 VDIG 接地时、电源序列与数据表图36中的序列 C 匹配。

e2e.ti.com/.../OPA564_5F00_Split_5F00_Supply_5F00_Sequence.TSC

希望这能把事情澄清一下。

谢谢。

扎赫