工具与软件:

我注意到 JFE2140的某些仿真中存在失真、并且每当漏栅电压升高到10V 以上时、将其缩小到异常大的栅极漏电流。 以下泄漏测试为导入 LTSpice 的 JFE2140使用 TI PSpice 模型。 该模型是否准确反映了可以预期的泄漏电流的类型? 是否需要连接/偏置保护二极管以减少泄漏? 我注意到、使用 LS844和2SK389BL 模型的仿真并没有显示几乎如此严重的泄漏。 谢谢! Scott。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

我注意到 JFE2140的某些仿真中存在失真、并且每当漏栅电压升高到10V 以上时、将其缩小到异常大的栅极漏电流。 以下泄漏测试为导入 LTSpice 的 JFE2140使用 TI PSpice 模型。 该模型是否准确反映了可以预期的泄漏电流的类型? 是否需要连接/偏置保护二极管以减少泄漏? 我注意到、使用 LS844和2SK389BL 模型的仿真并没有显示几乎如此严重的泄漏。 谢谢! Scott。

Scott、您好!

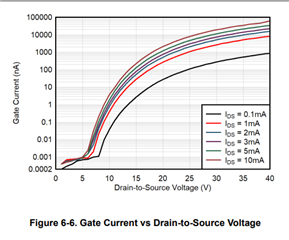

否未对漏电流建模以表示超过10V 的实际栅极漏电流。 数据表中的曲线是栅极泄漏的预期数据、也是测得的数据。 TI 将我们的器件建模为行为模型、而不是器件的确切副本。

例如、未对输入失调电压建模。 我们发布了一种可用于多种配置的模型、而不是在差分对配置中对输入失调电压进行建模的模型。 每个在 Tina 中都具有相同的 Vgs、但用户可以根据需要进行修改。

该模型中的二极管通过建模图6-6表示 JFE2140器件在10V 之后的 IG 泄漏。 由于工具限制和建模图6-6、该模型仅用于显示高达10V 时器件的可用性。 如下所示、10V 时仿真中的电流要高得多。 测量值是您在上面的图6-6中所示的真实器件中的预期值。 请注意、泄漏电流在测量值中也会流出、但由于 SPICE 的限制、模型无法准确反映器件测量结果。

建模行为

此致、

Chris Featherstone