Other Parts Discussed in Thread: TM4C123GH6PM, EK-TM4C1294XL

Thread 中讨论的其他器件: EK-TM4C1294XL

工具/软件:

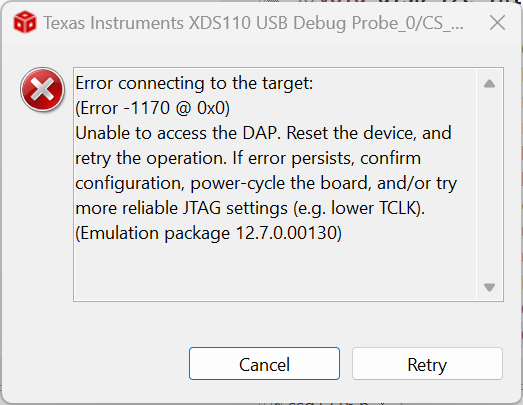

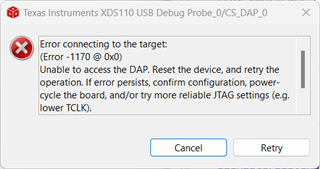

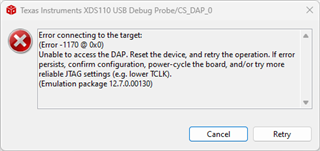

我在定制电路板上对 TM4C123GH6PM 进行编程时遇到问题。 我一直收到以下错误消息、

我已经尝试使用 dbgjtag.exe 重置 DAP、但其无效。

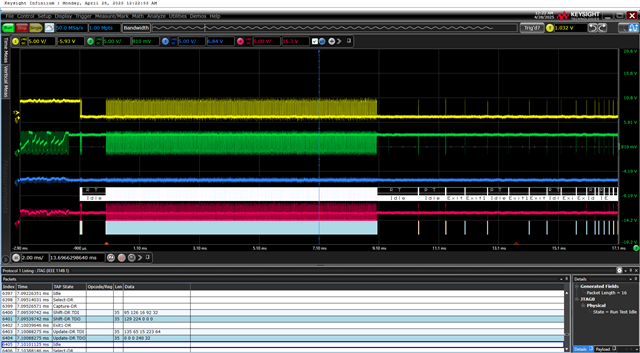

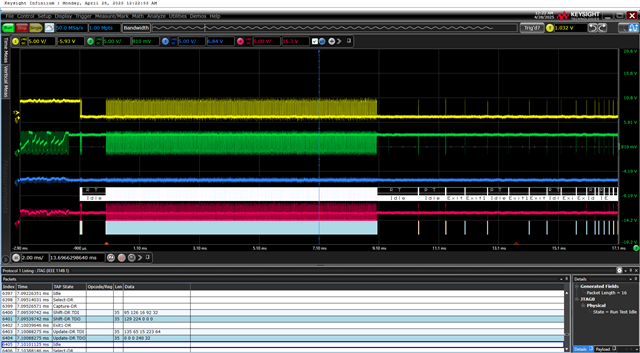

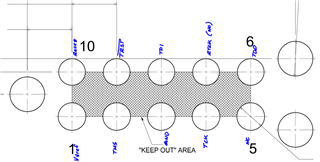

下面是 JTAG 接头的屏幕截图、

通道1 TMS、通道2 TCK、通道3 TDI、通道4 TDO。

来自协议解码的数据已附加。

谢谢、

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Other Parts Discussed in Thread: TM4C123GH6PM, EK-TM4C1294XL

工具/软件:

我在定制电路板上对 TM4C123GH6PM 进行编程时遇到问题。 我一直收到以下错误消息、

我已经尝试使用 dbgjtag.exe 重置 DAP、但其无效。

下面是 JTAG 接头的屏幕截图、

通道1 TMS、通道2 TCK、通道3 TDI、通道4 TDO。

来自协议解码的数据已附加。

谢谢、

嗨、Allan、

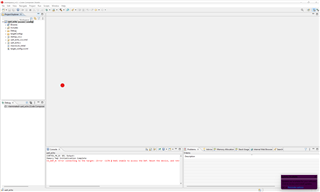

能否运行 JTAG 扫描链测试? 请参阅下面在 CCS 中的。 结果显示了什么?

还有其他调试探针吗? 是否可以对另一个探头重复相同的问题? 我想知道这是调试探针问题还是电路板问题。

我想这是您的定制板、对吧? 您有多少块电路板出现了 JTAG 连接问题? 我想知道这是否是一次性问题。

看起来您已尝试"解锁"操作、但仍然无法恢复设备。 如果是原始设备、解锁操作将不起作用。 解锁操作适用于以下情况:

-您已将设备置于深度睡眠或休眠模式,没有唤醒的机制。 如果没有正在运行的时钟、调试探针将无法与处理器同步。

-您的应用将 JTAG 引脚重新用于 GPIO。

-您已编程 BOOTCFG 寄存器以禁用 JTAG 接口。

如果上述情况均未发生、则解锁将不起作用。

另请参阅此应用手册 https://www.ti.com/lit/pdf/spma075 、该应用手册的第6节介绍了如何调试 JTAG 问题。 第4节提供了 JTAG 接头的各种示例原理图。 请与您的实现方案进行比较、看看您是否发现任何差异。

嗨、Allan、

扫描链测试看起来不错。 这证明 JTAG 接口在 TMS、TCK、TDI 和 TDO 连接方面是正常的。 您是否有 EK-TM4C1294XL LaunchPad? 上面有一个 pogo 标题。 您能尝试一下吗? 请记住、LaunchPad 上的 Pogo 接口用于连接到 ICDI 器件(由 TM4C12123器件枚举)、而不是目标 TM4C129器件。 如果能够连接、则可以在 CCS 中查看 ICDI 闪存内容。

尊敬的 Charles:

我有 EK-TM4C1294XL Launchpad。 我能够将一些导线焊接到电路板上的标签连接焊盘上。

JTAG 扫描测试通过、

[Start]

Execute the command:

%ccs_base%/common/uscif/dbgjtag -f %boarddatafile% -rv -o -S integrity

[Result]

-----[Print the board config pathname(s)]------------------------------------

C:\Users\User\AppData\Local\TEXASI~1\CCS\

ccs1271\0\0\BrdDat\testBoard.dat

-----[Print the reset-command software log-file]-----------------------------

This utility has selected a 100/110/510 class product.

This utility will load the adapter 'jioxds110.dll'.

The library build date was 'Apr 19 2024'.

The library build time was '14:04:01'.

The library package version is '12.7.0.00130'.

The library component version is '35.35.0.0'.

The controller does not use a programmable FPGA.

The controller has a version number of '5' (0x00000005).

The controller has an insertion length of '0' (0x00000000).

This utility will attempt to reset the controller.

This utility has successfully reset the controller.

-----[Print the reset-command hardware log-file]-----------------------------

The scan-path will be reset by toggling the JTAG TRST signal.

The controller is the XDS110 with USB interface.

The link from controller to target is direct (without cable).

The software is configured for XDS110 features.

The controller cannot monitor the value on the EMU[0] pin.

The controller cannot monitor the value on the EMU[1] pin.

The controller cannot control the timing on output pins.

The controller cannot control the timing on input pins.

The scan-path link-delay has been set to exactly '0' (0x0000).

-----[Perform the Integrity scan-test on the JTAG IR]------------------------

This test will use blocks of 64 32-bit words.

This test will be applied just once.

Do a test using 0xFFFFFFFF.

Scan tests: 1, skipped: 0, failed: 0

Do a test using 0x00000000.

Scan tests: 2, skipped: 0, failed: 0

Do a test using 0xFE03E0E2.

Scan tests: 3, skipped: 0, failed: 0

Do a test using 0x01FC1F1D.

Scan tests: 4, skipped: 0, failed: 0

Do a test using 0x5533CCAA.

Scan tests: 5, skipped: 0, failed: 0

Do a test using 0xAACC3355.

Scan tests: 6, skipped: 0, failed: 0

All of the values were scanned correctly.

The JTAG IR Integrity scan-test has succeeded.

-----[Perform the Integrity scan-test on the JTAG DR]------------------------

This test will use blocks of 64 32-bit words.

This test will be applied just once.

Do a test using 0xFFFFFFFF.

Scan tests: 1, skipped: 0, failed: 0

Do a test using 0x00000000.

Scan tests: 2, skipped: 0, failed: 0

Do a test using 0xFE03E0E2.

Scan tests: 3, skipped: 0, failed: 0

Do a test using 0x01FC1F1D.

Scan tests: 4, skipped: 0, failed: 0

Do a test using 0x5533CCAA.

Scan tests: 5, skipped: 0, failed: 0

Do a test using 0xAACC3355.

Scan tests: 6, skipped: 0, failed: 0

All of the values were scanned correctly.

The JTAG DR Integrity scan-test has succeeded.

[End]

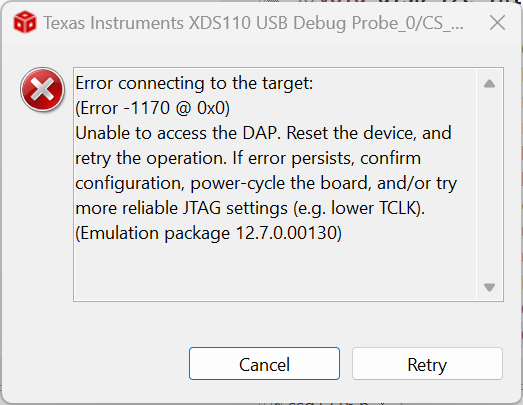

但是、当我尝试 连接到 MCU 时收到与之前相同的错误消息、

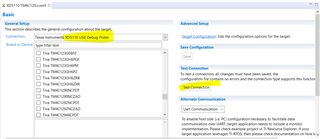

我的连接设置如下所示、

我已删除 USB 集线器和 Thunderbolt 坞站、但仍然收到无法访问 DAP 错误消息。

我还尝试连接 XDS100V2、但得到"Cable break (电缆断开)"错误消息。

[Start]

Execute the command:

%ccs_base%/common/uscif/dbgjtag -f %boarddatafile% -rv -o -F inform,logfile=yes -S pathlength -S integrity

[Result]

-----[Print the board config pathname(s)]------------------------------------

C:\Users\User\AppData\Local\TEXASI~1\CCS\

ccs1271\0\0\BrdDat\testBoard.dat

-----[Print the reset-command software log-file]-----------------------------

This utility has selected a 100/110/510 class product.

This utility will load the adapter 'jioserdesusb.dll'.

The library build date was 'Apr 19 2024'.

The library build time was '14:04:01'.

The library package version is '12.7.0.00130'.

The library component version is '35.35.0.0'.

The controller does not use a programmable FPGA.

The controller has a version number of '4' (0x00000004).

The controller has an insertion length of '0' (0x00000000).

This utility will attempt to reset the controller.

This utility has successfully reset the controller.

-----[Print the reset-command hardware log-file]-----------------------------

The scan-path will be reset by toggling the JTAG TRST signal.

The controller is the FTDI FT2232 with USB interface.

The link from controller to target is direct (without cable).

The software is configured for FTDI FT2232 features.

The controller cannot monitor the value on the EMU[0] pin.

The controller cannot monitor the value on the EMU[1] pin.

The controller cannot control the timing on output pins.

The controller cannot control the timing on input pins.

The scan-path link-delay has been set to exactly '0' (0x0000).

-----[The log-file for the JTAG TCLK output generated from the PLL]----------

There is no hardware for programming the JTAG TCLK frequency.

-----[Measure the source and frequency of the final JTAG TCLKR input]--------

There is no hardware for measuring the JTAG TCLK frequency.

-----[Perform the standard path-length test on the JTAG IR and DR]-----------

This path-length test uses blocks of 64 32-bit words.

The JTAG IR instruction path-length was not recorded.

-----[Perform the Integrity scan-test on the JTAG IR]------------------------

This test will use blocks of 64 32-bit words.

This test will be applied just once.

Do a test using 0xFFFFFFFF.

Scan tests: 1, skipped: 0, failed: 0

-----[An error has occurred and this utility has aborted]--------------------

This error is generated by TI's USCIF driver or utilities.

The value is '-183' (0xffffff49).

The title is 'SC_ERR_CTL_CBL_BREAK_FAR'.

The explanation is:

The controller has detected a cable break far-from itself.

The user must connect the cable/pod to the target.

[End]

谢谢、

Allan

尊敬的 Charles:

我还尝试使用 uart_echo 示例调试定制电路板、以防我的工程损坏。

我仍然收到同样的"Unable to access the DAP error message"。

JTAG 扫描测试通过 XDS110。

[Start]

Execute the command:

%ccs_base%/common/uscif/dbgjtag -f %boarddatafile% -rv -o -S integrity

[Result]

-----[Print the board config pathname(s)]------------------------------------

C:\Users\User\AppData\Local\TEXASI~1\CCS\

ccs1271\0\0\BrdDat\testBoard.dat

-----[Print the reset-command software log-file]-----------------------------

This utility has selected a 100/110/510 class product.

This utility will load the adapter 'jioxds110.dll'.

The library build date was 'Apr 19 2024'.

The library build time was '14:04:01'.

The library package version is '12.7.0.00130'.

The library component version is '35.35.0.0'.

The controller does not use a programmable FPGA.

The controller has a version number of '5' (0x00000005).

The controller has an insertion length of '0' (0x00000000).

This utility will attempt to reset the controller.

This utility has successfully reset the controller.

-----[Print the reset-command hardware log-file]-----------------------------

The scan-path will be reset by toggling the JTAG TRST signal.

The controller is the XDS110 with USB interface.

The link from controller to target is direct (without cable).

The software is configured for XDS110 features.

The controller cannot monitor the value on the EMU[0] pin.

The controller cannot monitor the value on the EMU[1] pin.

The controller cannot control the timing on output pins.

The controller cannot control the timing on input pins.

The scan-path link-delay has been set to exactly '0' (0x0000).

-----[Perform the Integrity scan-test on the JTAG IR]------------------------

This test will use blocks of 64 32-bit words.

This test will be applied just once.

Do a test using 0xFFFFFFFF.

Scan tests: 1, skipped: 0, failed: 0

Do a test using 0x00000000.

Scan tests: 2, skipped: 0, failed: 0

Do a test using 0xFE03E0E2.

Scan tests: 3, skipped: 0, failed: 0

Do a test using 0x01FC1F1D.

Scan tests: 4, skipped: 0, failed: 0

Do a test using 0x5533CCAA.

Scan tests: 5, skipped: 0, failed: 0

Do a test using 0xAACC3355.

Scan tests: 6, skipped: 0, failed: 0

All of the values were scanned correctly.

The JTAG IR Integrity scan-test has succeeded.

-----[Perform the Integrity scan-test on the JTAG DR]------------------------

This test will use blocks of 64 32-bit words.

This test will be applied just once.

Do a test using 0xFFFFFFFF.

Scan tests: 1, skipped: 0, failed: 0

Do a test using 0x00000000.

Scan tests: 2, skipped: 0, failed: 0

Do a test using 0xFE03E0E2.

Scan tests: 3, skipped: 0, failed: 0

Do a test using 0x01FC1F1D.

Scan tests: 4, skipped: 0, failed: 0

Do a test using 0x5533CCAA.

Scan tests: 5, skipped: 0, failed: 0

Do a test using 0xAACC3355.

Scan tests: 6, skipped: 0, failed: 0

All of the values were scanned correctly.

The JTAG DR Integrity scan-test has succeeded.

[End]

谢谢、

Allan