工具/软件:

您好、

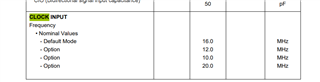

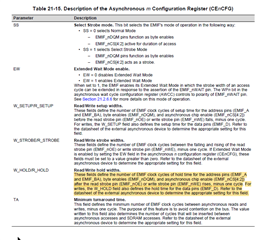

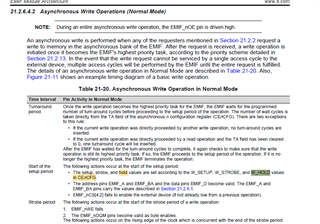

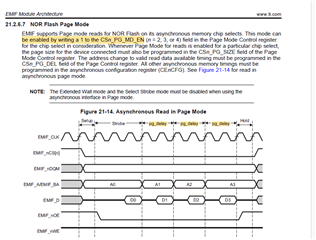

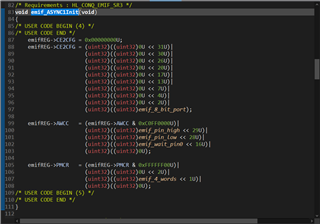

我目前在写入操作期间遇到 EMIF 问题。 我的目标是实现 EMIF 的最大速度、为此、我在异步配置寄存器(CE2CFG)中配置了尽可能低的时序。 具体来说、我已将写入和读取设置、选通和保持时间设置为0。

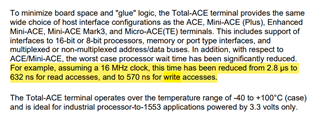

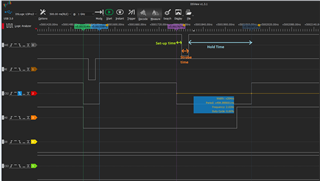

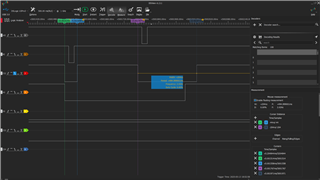

根据此配置、对于读取和写入操作、将一字节数据写入外部异步存储器的预期时间应约为40ns。 但在实践中、我观察到写入操作大约需要220ns、明显高于配置的值。 另一方面、读取时序接近约44ns 的预期值。

我附上了逻辑分析仪捕获结果和 EMIF 配置屏幕截图以供您参考。

您能否帮助我确定这种差异的原因、并建议可能的解决方案以实现所需的写入性能?

谢谢、

此致、

Veerappan P.