Other Parts Discussed in Thread: TM4C129ENCPDT

工具/软件:

我有一个 TM4C129ENCPDT 处理器以 60MHz 采样电压运行、形成铅酸电池、样本非常尖峰。

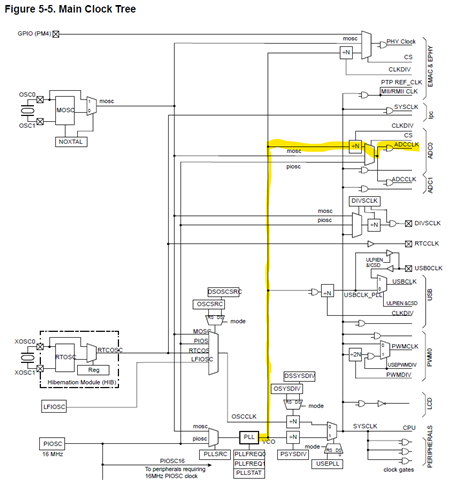

我使用精密 3V 基准、并在 15MHz 上运行 ADC 时钟。

启用硬件过采样或增加采样保持周期似乎没有什么区别。

以下是使用 15MHz 采样时钟且无硬件过样(蓝色)时的默认样本设置捕获、然后是使用 32 个硬件样本(橙色)时的相同波形样本。

如果我将外部 Arduino 处理器连接到相同的电压、我会得到一个干净的波形、请参见下面的蓝色波形。

我添加了一些代码、允许我指定 ADC 时钟并根据我的系统时钟 60MHz 计算适当的分频值

ADCdivisor = ui32SysClock / ADC_CLK_SPEED;

ADCrate = ADC_CLOCK_RATE_FULL;

ADCclock = ui32SysClock / ADCdivisor;

if (ADCdivisor > 64)

{

ADCrate = ADC_CLOCK_RATE_HALF;

ADCdivisor = ui32SysClock / ADC_CLK_SPEED / 2;

ADCclock = ui32SysClock / ADCdivisor / 2;

if (ADCdivisor > 64)

{

ADCrate = ADC_CLOCK_RATE_FOURTH;

ADCdivisor = ui32SysClock / ADC_CLK_SPEED / 4;

ADCclock = ui32SysClock / ADCdivisor / 4;

if (ADCdivisor > 64)

{

ADCrate = ADC_CLOCK_RATE_EIGHTH;

ADCdivisor = ui32SysClock / ADC_CLK_SPEED / 8;

if (ADCdivisor > 64)

{

ADCdivisor = 64;

}

ADCclock = ui32SysClock / ADCdivisor / 8;

}

}

}

else if (ADCdivisor == 0)

{

ADCdivisor = 1;

ADCclock = ui32SysClock;

}

rprintf("Sysclock %d Divisor %d ADC Clock %d\r\n", ui32SysClock, ADCdivisor, ADCclock);

// ADC Clock can only be set on

ADCClockConfigSet(ADC0_BASE, ADC_CLOCK_SRC_PLL | ADCrate, ADCdivisor);

ADC 初始化为

// Initialisation ADCClockConfigSet(ADC0_BASE, ADC_CLOCK_SRC_PLL | ADCrate, ADCdivisor); ADCHardwareOversampleConfigure(ADC0_BASE, 32); ADCSequenceDisable(ADC0_BASE, 1); ADCSequenceConfigure(ADC0_BASE, 1, ADC_TRIGGER_PROCESSOR, 0); ADCSequenceStepConfigure(ADC0_BASE, 1, 0, ADC_CTL_CH13 | ADC_CTL_IE | ADC_CTL_END); // Battery Volts ADCSequenceEnable(ADC0_BASE, 1); //Enable the ADC

采样循环重复以下内容:

ADCIntClear(ADC0_BASE, 1); //Clear Interrupt to proceed to next data capture

ADCProcessorTrigger(ADC0_BASE, 1); //Ask processor to trigger ADC

if (ADCIntStatus(ADC0_BASE, 1, false))

{

ADCSequenceDataGet(ADC0_BASE, 1, RawAnalogOther);

}

我尝试一次只更改一个参数、但没有看到尖峰有任何改善。

我按如下方式应用采样保持:

ADCSequenceStepConfigure(ADC0_BASE, 1, 0, ADC_CTL_CH13 | ADC_CTL_SHOLD_16);

ADCHardwareOversampleConfigure(ADC0_BASE, 32);

硬件过采样 0...64 几乎没有区别

ADC_CTL_shold 2...256 没有什么区别。

从 1MHz 到 10MHz 的时钟速度几乎没有区别。

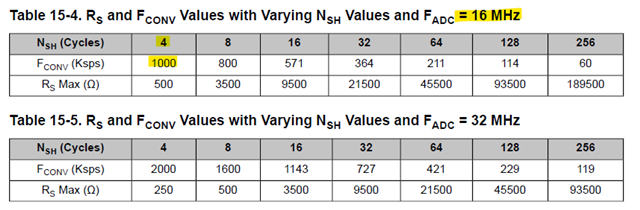

有趣的是、当我为时钟设置 15MHz 或更高频率时、电压输出从 910 下降到 524、这似乎表明采样保持时间不够长。

不过、电压在 4 个时钟的采样保持时间或 256 个时钟的采样保持时间内保持在这个半电平、无论我使用什么采样保持时间、电压都保持在半电平。

将时钟向下更改为 10MHz、即使采样保持时间为 4 个时钟、电压也是正确的。

看起来没有应用采样保持。

对于如何提高输出有何建议?