Thread 中讨论的其他器件: LP-AM261、 SysConfig

工具/软件:

您好、

客户现在正在使用 LP-AM261 评估 AM2612。

它们考虑将 25MHz 晶体振荡器连接到 EXT_REFCLK0。

EXT_REFCLK0 的引脚可以通过高达 100MHz 的输入。 正确?

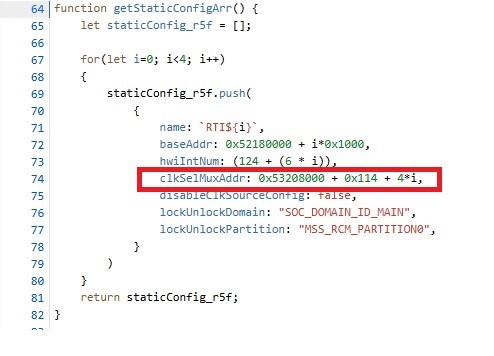

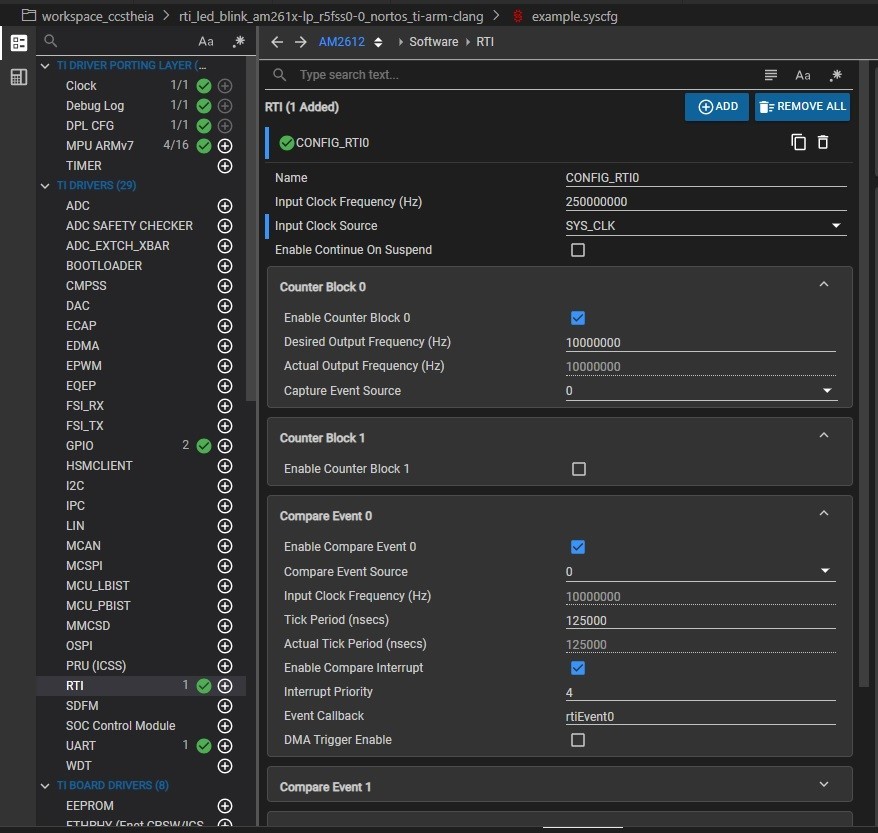

它们通过以下配置评估计时器中断、并使用示波器观察计时器中断周期。 它将是 125us 的计时器中断周期。

当 AM2612 通过 DEVBOOT 模式启动时、他们可以按预期观察到 125us 的计时器中断周期。

但是、当使用 OSPI 引导模式启动时、它将有 1250 μ s。 它的周期比预期的长 1000 倍。

您是否有任何解决方案来解决此问题?

谢谢。此致、

英明