Other Parts Discussed in Thread: HALCOGEN, TMS570LC4357

Thread 中讨论的其他器件:HALCOGEN、 TMS570LC4357

工具/软件:

我有 PGE(144 引脚)版本的芯片(如果重要)。 SPI5 ENA 出现在引脚 97 上(如果您设置了正确的引脚多路复用器)。 但对我来说、引脚 97 尚未连接。 我想确保我可以将 ENA 用作 GIO 引脚、但无法与 HalCoGen 配合使用。 我写了以下代码:

spiREG5->PC0 = 0;

spiREG5->PC1 = 0xfff;

spiREG5->PC3 = 0;

printf(“SPI5 After 0 to PC3:PC0:%x、PC1:%x、PC2:%x、PC3:%x\n“、spiREG5->PC0、spiREG5->PC1、spiREG5->PC2、spiREG5->PC3);

spiREG5->PC4 = 0xfff;

printf (fff 到 PC4 后的“SPI5:PC0:%x、PC1:%x、PC2:%x、PC3:%x\n“、spiREG5->PC0、spiREG5->PC1、spiREG5->PC2、spiREG5->PC3);

printf(“Single bits Ena and Clock:%d %d\n“、gioGetBit (spiPORT5、8)、gioGetBit (spiPORT5、9));

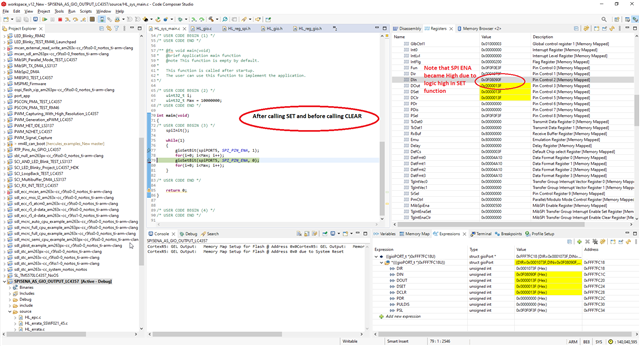

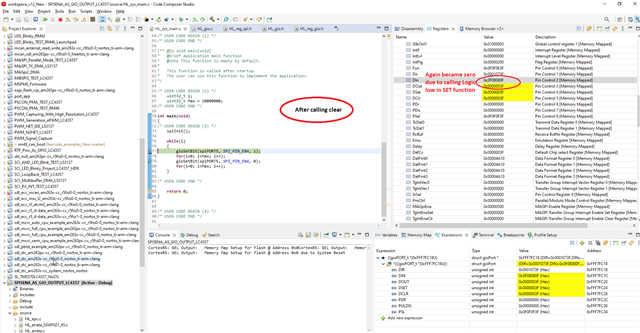

结果是:

在 0 到 PC3 之后的 SPI5:PC0:0、PC1:1010f0f、PC2:0、PC3:0

从 fff 到 PC4 后的 SPI5:PC0:0、PC1:1010f0f、PC2:1010e0f、PC3:1010f0f

Single-bit Ena 和时钟:0 1

换句话说、对于所有 SPI5 引脚、PC0 被设置 为 GIO、对于从 SCS0 至 SOMI0(以及一个未使用的)引脚的所有引脚、PC1 被设置为输出。 向 DOUT 写入 1 实际上会设置所有位

为 DOUT 读回时的传播延迟。 但是、鉴于这是一个输入/输出 GIO、我希望在 DIN 上获得相同的结果、实际上我会对所有实现的 SCS 线路执行相同的结果

和时钟线。 但未启用。 遗憾的是、我需要另一个 GIO 引脚、使能引脚是封装上可用的引脚。 为什么它与其余的所有 SPI 引脚都不同?