工具/软件:

尊敬的专家:

我想回顾一下之前讨论过的一个主题、但我认为仍然缺乏决定性答案:

AM2431:XIP 存储器映射写入 (MRAM)

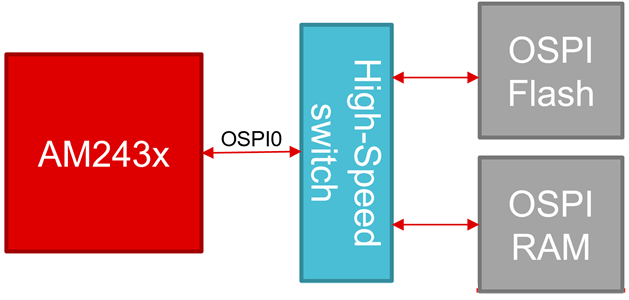

问题在于 OSPI 外设(基本上在 ALX 上作为四路 SPI 运行)是否可用于实现对外部 SPI PSRAM 的完全存储器映射访问。

具体而言、我的目标是直接通过指针读取和写入外部 RAM 上的变量、就像标准存储器一样。

典型的 Flash-XIP 用例中明确支持存储器映射读取。 然而,根据章节 12.3.2.4.9. OSPI 直接访问控制器 (DAC) 、也可以进行内存映射写入:

直接访问是指数据接口访问直接触发对闪存存储器读取或写入的操作。 它采用存储器映射、可用于从外部闪存访问和直接执行代码。

闪存所需的扇区擦除通过 STIG 手动完成、因此如果连接 PSRAM、可以轻松省略该操作。

例如、我正在考虑使用 PSRAM 芯片、比如此处所示的“四通道 RAM“: https://www.issi.com/ww/pdf/SerialRAM.pdf

它支持与闪存兼容的 SPI 接口、这意味着从 OSPI 外设生成的操作码应兼容:

具有 DS NOR 闪存兼容接口的 JEDEC 标准四路 I/O (4S-4D-4D)

从理论上讲、这种设置是可行的、但我非常想倾听 TI 专家或任何尝试过这种设置的人的心声。

是否有人使用 OSPI 成功实现了对外部 SPI PSRAM 的存储器映射读取/写入访问?

此外、我不确定 CPU 和高速缓存控制器是否按照我想要的方式完全支持此模式、特别是对外部 RAM 进行基于指针的无缝访问。

这一功能将成为 Sitara 控制器的一项显著优势。 2MB 的内部 SRAM 不足以满足我们的应用需求、因此我们不能使用支持 DRAM 和 GPMC 的更大 ALV 封装。

虽然闪存中的 XIP 有助于重定位代码、但我们的主要需求是为大型数据缓冲区扩展 RAM、从而使外部 PSRAM 成为潜在的理想解决方案。

提前感谢您的见解和经验!

此致、

Stefan