工具/软件:

尊敬的团队:

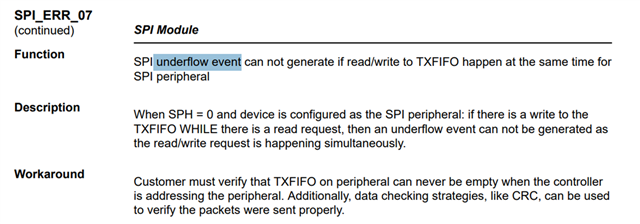

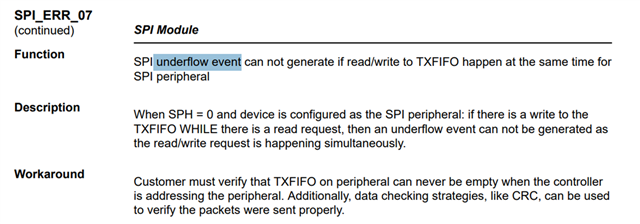

我的客户使用 M0G1506 作为 SPI 从器件、但在第一次传输时没有填充 TX FIFO。 但是 M0G1507 接收到错误的数据(由 CRC 检查),为什么会发生这种情况?

理论上、从器件可以接收正确的数据。

此致、

Zane

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

尊敬的团队:

我的客户使用 M0G1506 作为 SPI 从器件、但在第一次传输时没有填充 TX FIFO。 但是 M0G1507 接收到错误的数据(由 CRC 检查),为什么会发生这种情况?

理论上、从器件可以接收正确的数据。

此致、

Zane

尊敬的 Sal:

我的客户使用 FPGA 实现 SPI 作为控制器、它将控制 64 个 CLK 并使用 FIFO 来接收 64 位。 并使用空闲中断将其读出。

请查看客户描述:

e2e.ti.com/.../SPI_EE959898_.docx

我尝试重现客户的问题。 我使用空闲中断来读取 FIFO 数据、我发现有时它会得到错误的数据。

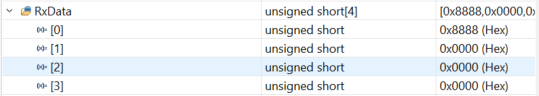

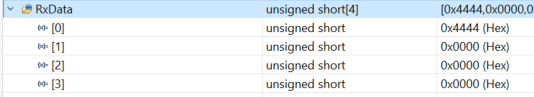

我发送 0x8888 (1000 1000 1000 1000)、但有时我收到 0x4444(0100 0100 0100)、似乎换档效果不佳。

我连接了工程、这可以很容易重现此问题、但将 NRST 引脚推入控制器中、并可以在从服务器调试窗口中查看 Rxdata。 请帮助找到它,谢谢!

e2e.ti.com/.../8244.spi_5F00_controller_5F00_multibyte_5F00_fifo_5F00_poll_5F00_LP_5F00_MSPM0G3507_5F00_nortos_5F00_ticlang.zipe2e.ti.com/.../spi_5F00_peripheral_5F00_multibyte_5F00_fifo_5F00_poll_5F00_LP_5F00_MSPM0G3507_5F00_nortos_5F00_ticlang.zip

此致、

Zane

尊敬的 Zane:

我根据您的反馈进行了一些测试、如果用户填写或未填写数据、我认为不会产生影响。

我甚至没有将任何数据填充到 TXDATA、所有数据看起来都很好。

在我看来、使用空闲中断不是一个好主意、因为当 SPI BUSY 变为低电平时会设置空闲状态。

如果 TX FIFO 中有数据、SPI BUSY 不会变为低电平。 数据处理可能存在风险、然后会丢失一些 Rx 数据。

如果您只有 4 个 16 位数据、建议使用 RX 中断或 Rx FULL;请参阅我验证它在 1MHz 模式下工作而没有任何问题的示例。

LP_MSPM0G3507_SPI_TX_Master.ZIP

我发送 0x8888 (1000 1000 1000 1000 1000)、但有时我收到 0x4444(0100 0100 0100)、似乎移位效果不好。

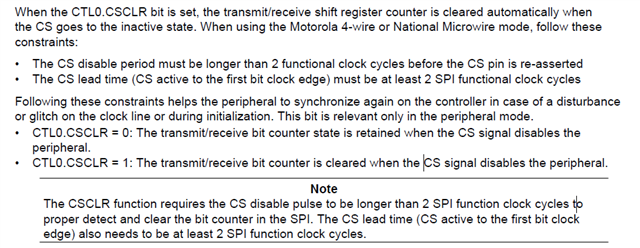

请检查您 CS 信号、因为 CS 信号正常工作、然后在 CS 保持非活动状态时、移位器寄存器计数器将自动清除。 虽然 CS 信号存在一些限制:

B.R.

Sal

尊敬的 Zane:

更新了测试项目以供参考: rx_test_new_ZIP

当 TXFIFO 中没有数据(仅在第一次发送中显示)时、此工程还会创建 RX 接收数据错误。

看起来、CSCLR 功能需要设置为 0h、以便在 CS 处于非活动状态时启用自动清除移位器寄存器。 详情请参阅电子邮件。

B.R.

Sal