“线程”中讨论的其它部件:测试, HALCOGEN,

尊敬的 TI 专家:

我们正在尝试通过 EMIF 模块在定制板上连接 ISSI IS42S16100H-7TLI。

我们正在使用 PLL1 (180 MHz)和 EMIF (90 MHz)操作 CPU。 在连续写入 SDRAM 的过程中,我们注意到每秒只有第三个单元被正确写入一次。 当我们将 CPU 频率降低到90 MHz,使 f_cpu = f_EMIF = 90 MHz 时,连续写入 SDRAM 的工作几乎达到100%。 读取操作似乎独立于频率设置。

测试代码:

__attribute__((section(".farbss"))) volatile uint16_t sdram_far[100] = { 0 }; // test array in sdram

/**

* main.c

*/

int main(void)

{

uint16_t sdram_read[100] = { 0 };

// write to sdram far memory

for(uint16_t i = 0; i < 100; i++)

{

sdram_far[i] = i;

}

// reading from sdram

for(uint16_t i = 0; i < 100; i++)

{

sdram_read[i] = sdram_far[i];

}

}

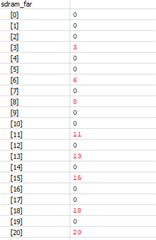

案例1:F_CPU = 180 MHz,F_EMIF = 90 MHz 案例2:F_CPU = F_EMIF = 90 MHz (仅忽略单元格3的写入)

壁龛中的定时设置:

我们怀疑,在案例1中,我们的 EMIF 带宽过大。 那么,当 f_CPU > f_EMIF 时,如何从软件端连续访问 SDRAM 内存? TMS570LS1114是否有我们可以遵循的应用说明?

我们正在开展一个大型客户项目,我们非常感谢您的帮助。

此致

大卫