主题中讨论的其他器件:TM4C123、 EK-TM4C1294XL

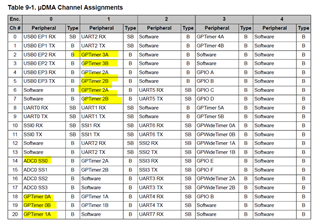

我使用4个计时器作为 PWM 模式。

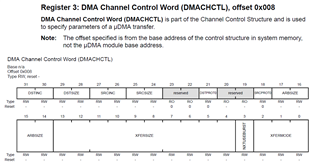

每个定时器都有自己的 DMA 中断信号来将1个项目从内存传输到自己的匹配寄存器来改变占空比。

这运行正常。 但当我激活 UDMA 以进行 ADC 采样到存储器时。 我的计时器 PWM 信号有时不会在一个 PWM 周期内运行。

为什么? 我对它进行了大量测试、以找到误差。 我的想法不好。

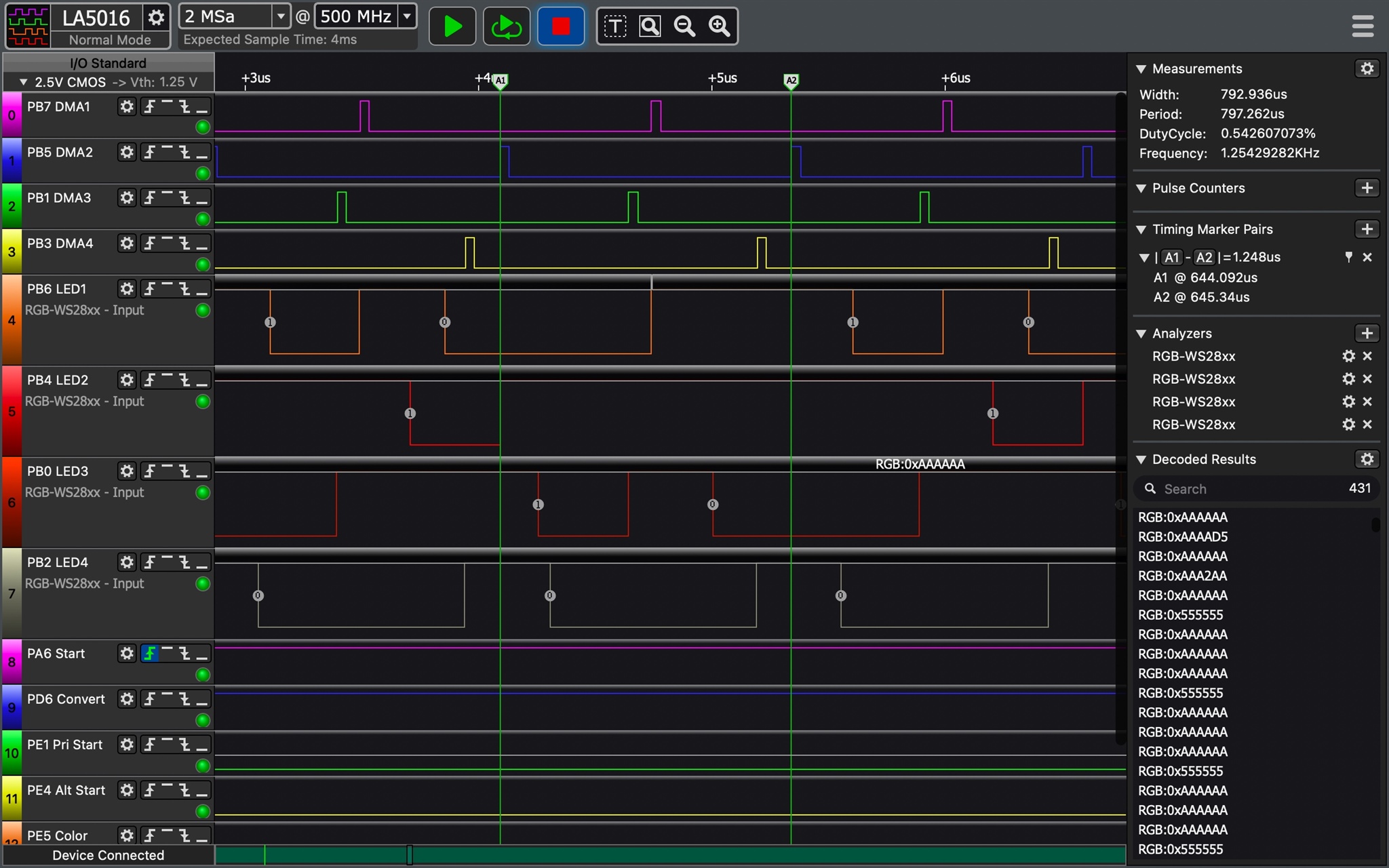

这是一张图片。 故障发生在通道5 PB4 LED2上。 周期内的周期完全为高电平。 当 UDMA 信号延迟时、匹配寄存器中的值较旧。

邮政编码是否有用? 超过3000行代码的应用。