请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TMS570LC4357 主题中讨论的其他器件:HALCOGEN

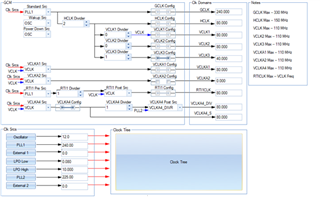

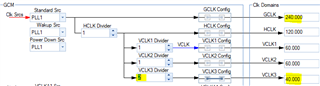

我正在尝试使用300MHz CPU 时钟(GCLK)和40MHz EMIF 时钟设置570LC4357时钟(由于具有40MHz 时钟的一次性可编程 FPGA、此设置无法更改)。 我从 HALCoGen 工具中可以看到、EMIF 总线连接到 VCLK3、VCLK 由与 GCLK 相同的 PLL 输出驱动、因此我无法选择为 VCLK3生成40MHz、为 GCLK 生成300MHz。

是否有任何未记录的功能可以实现此技巧? 下面是我在 HALCoGen 中拥有的内容。