主题中讨论的其他器件:TM4C1290NCPDT

我没有疑问、但想对相关问题(该主题现已锁定)中提出的问题提供可能的解释。 也许 TI 的某个人可以确认或拒绝这一点、并提供数据表中所述内容以外的一些详细信息。

Brad Rodriguez (OP)写道:"此时、我使用 TM4C 计时器生成一个常规的50微秒脉冲、在前缘触发、并使用数字'scope 观察后缘。 我看到后沿上的抖动约为8ns、其中2.5ns 可归因于"范围"。

Randy OTT 写道:"我不会太快地将观察到的抖动归咎于 PLL。 8nS 非常接近120MHz 时钟的8.333nS 周期... PLL 实际上不应产生太大的抖动。"

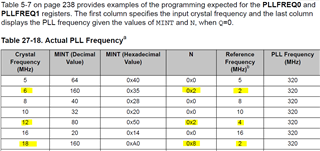

TLDR -我认为抖动的根本原因是使用晶体频率(25MHz)、而该频率不是320MHz 或480MHz 的精确分频值。 如果使用整数除数晶体频率、例如5MHz、10MHz 或16MHz、我怀疑抖动会大大减少。

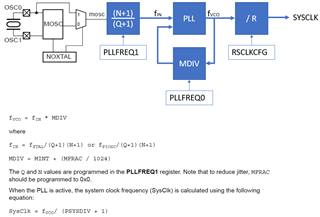

为什么晶体频率很重要? 它归结为 PLL 的工作原理、在本例中为分数 N PLL。 PLL 处理控制 VCO 生成的频率的电压。 它通过比较两个信号(一个来自基准、一个来自反馈)的相位并进行调整以使其保持锁相(因此称为"锁相环")、从而使频率相等来实现这一目的。 为了从 VCO 获得比基准更高的频率(在本例中来自晶体)、在 VCO 输出和相位比较器之间的反馈环路中插入了一个分频器。 例如、如果将分频器设置为将频率降低10倍、则分频版本的 VCO 频率必须是参考频率的10倍、该参考频率将到达相位比较器、以等于参考频率。 因此分频器(在反馈环路中)可以有效地将 VCO 输出频率设置为基准的倍数、在本例中为10X。 这一切都非常简单(在概念上)、正如 Randy 所写的、不应导致 VCO 输出产生太多抖动。

当您希望输出频率是基准的某个非整数倍时、它会变得更加复杂。 一个选项是在基准频率到达相位比较器之前对其进行分频(预分频)、然后乘以一个较大的因子以获得输出。 我一直无法确定 TM4C129是否能够做到这一点。 如果可以的话、25MHz 基准可以除以5、然后乘以整数、以达到 VCO 支持的频率320MHz 或480MHz (然后除以得到120MHz 或任何系统时钟)。 我认为这也会提供低抖动输出。

不过、在这种情况下、我可能会使用不同的技术、在反馈环路中使用小数(实际上是混合数)除数、这是由"小数 N" PLL 支持的。 查看 _SysCtlFrequencyGet 的源代码、它看起来好像有一个可用的/32 (5位)小数(可能还有一个/1024)。 假设一个数字比实际数字更好的示例、假设我们有一个16.384MHz 晶体(在 SYSCTL.h 中定义为 SYSCTL_XTAL_16_3MHz)、并希望 VCO 输出320MHz。 这意味着我们需要在 PLL 的反馈环路中实现19.53125的分压比。 这恰好是19 17/32、因此它非常适合/32分数 N PLL。 每次脉冲进入分频器时、输出会改变或不改变;那里没有分次可用。 因此、它将部分时间除以19、其余时间除以20 (时间的17/32)、因此平均 分频比得到了正确的结果。 现在应该很明显、当使用分数(而不是整数)比时、输出中会出现抖动;分频器分频比以及因此输出频率在可用频率阶跃(基准频率的倍数)之间不断变化、以获得所需的平均频率。

分压器比率变化引起的这种变化可以通过在相位比较器输出达到 VCO 之前对模拟电压输出进行滤波来得到一定程度的平滑、因此 VCO 输出不会对变化进行密切跟踪。 搜索"PLL 环路滤波器"以了解更多相关信息(它会变得非常复杂)。 在这种情况下、PLL 环路滤波器位于 MCU 内部、无法更改。 但它 确实会影响输出跟踪不规则分频器输出的紧密程度、因此使得诸如8ns 抖动(在 OP 示例中)接近120MHz 时钟的8.333ns 周期的观察与分频器的运行没有直接关系。 我不确定这些特定数字是否只是重合、但我确信使用小数分频器会在时域中引入抖动、并在频域中引入相应的"有趣"(不良)影响。

我所写的内容是否适用于本例、主要是猜测、但它似乎符合 OP 的观察结果以及我能够从源代码和数据表中解密的内容。 如果 TM4C129数据表包含一个方框图、其中显示了 PLL 与预分频器的内部关系(如果有的话)、并且显示了反馈环路分频器、这将是很好的、这样我们就可以更好地探索折衷并了解建议的寄存器值。

Steve

P.S. 我偶然发现了 Wikipedia 页面上的"双模预分频器"。 它的工作原理与我描述的非常相似、但在达到相位比较器之前应用于基准频率。 我不熟悉此类预分频器、但它们似乎不可避免地以类似的方式引入抖动。 我知道、TM4C129可能会在反馈环路中使用其中一个、而不是或以及分数 N 分频器。