您好!

这是一个有关强制生成 ESM1.26的问题。

我们现在在评估板上测试 TMS570 MCU 的 ESM 功能。

根据 SPNU563A 第8.2.2.4节所述内容、为了生成 ESM1.26、我们认为 L2RAMW 中 RAMERRSTATUS 寄存器的 CPUWE (0)是错误源之一。

要验证 ESM1.26的通知、您能否告诉我强制生成 ESM1.26的技术?

谢谢、

好的

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

这是一个有关强制生成 ESM1.26的问题。

我们现在在评估板上测试 TMS570 MCU 的 ESM 功能。

根据 SPNU563A 第8.2.2.4节所述内容、为了生成 ESM1.26、我们认为 L2RAMW 中 RAMERRSTATUS 寄存器的 CPUWE (0)是错误源之一。

要验证 ESM1.26的通知、您能否告诉我强制生成 ESM1.26的技术?

谢谢、

好的

大家好、Kobori-San、

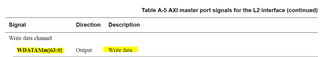

当 CPU 写入 L2RAMW 并导致 L2RAMW 检测到单一位 ECC 错误时、CPUWE 位被置位。 让我简要解释一下 CPU 写入事务。 当 CPU (例如 Cortex-R5F 内核)写入 L2RAMW 时、它将驱动其 WDATAMm[63:0]总线上的64位数据。 它还将驱动 WERRCODEMm[7:0]总线上相应数据的 ECC 代码。 请查找以下信号。 如果您想详细了解整个 Cortex-R5 AXI 接口信号、请访问 https://developer.arm.com/documentation/ddi0460/d 上的 Cortex-R5 TRM。

当 L2RAMW 接收到来自主设备的写请求时、它将为 WDATAMm 总线上的数据计算自己的 ECC。 然后根据 WERRCODEMm 上接收到的 ECC 来检查计算出的 ECC。 这基本上就是 ECC 检查的工作方式、我认为这一点很清楚。

现在、您的问题是如何"强制" ECC 可纠正的错误、以便 CPUWE 位和 ESM 1.26将被置位。 这实际上是不可能的、因为这是 CPU 上的运行时诊断检查。 只有当 L2RAMW 计算出的 ECC 与 WERRCODEMn 不同时、CPUWE 和 ESM 1.26才会被置位。 Cortex-R5中没有机制在简单的工作台上强制 WDATAMn 或 WERRCODEMn 总线上进行位翻转。

如果您运行8.2.6中概述的诊断测试、则如果 DWSE 标志(即 RAMERRSTATUS 寄存器的位19 )未通过写入事务的单个位错误诊断、则可以设置该标志。