主题中讨论的其他器件:RM46L852、

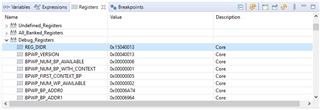

我的问题是针对任何 TMS 或其他 TI 基于 ARM 的 SoC:哪个数据表将包含可用/实现的硬件断点和观察点的实际数量(单独)?

因此、从 ARM 的文档中:

https://developer.arm.com/documentation/ddi0363/g/Functional-Description/About-the-functions/Debug

显示"...在执行期间配置断点和观察点的数量、请参阅 可配置选项。 "、 对于 断点、显示在2 - 8范围内的任何位置。

https://developer.arm.com/documentation/ddi0363/g/Introduction/Configurable-options?lang=en

我在 TMS570x 数据表中看不到专门为这些配置的内容。 TI 在何处记录此内容?