是否可以使用连接到 MIBSPI5的四路 SPI 器件。

我看到他们谈论的是并行模式2-2、4-4、8-8....

我有 一个 S70FL01GS (双512Mbit) SPI 存储器、我可以作为2个独立芯片运行、也可以在四通道模式下运行...

只是不确定是否在 HERC 参考手册中描述了"并行模式"(第 28.2.6.6.6.5节...SPNU563A–2018年3月)

一如既往地感谢您的回应

谢谢!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

是否可以使用连接到 MIBSPI5的四路 SPI 器件。

我看到他们谈论的是并行模式2-2、4-4、8-8....

我有 一个 S70FL01GS (双512Mbit) SPI 存储器、我可以作为2个独立芯片运行、也可以在四通道模式下运行...

只是不确定是否在 HERC 参考手册中描述了"并行模式"(第 28.2.6.6.6.5节...SPNU563A–2018年3月)

一如既往地感谢您的回应

谢谢!

您好!

串行四路 SPI 协议使用 4个引脚(IO[3:0])发送和接收、这是半双工的。 MibSPI 并行使用4条线(SIMO[3:0])发送和分离4条线(SOMI[3:0])接收、即全双工。

要使用 S70FL01GS 闪存、您需要 通过4个引脚发送命令/地址/数据。 有用于写入、读取和擦除操作的预定义命令。 要将全双工转换为半双工、您可能需要外部电路来切换发送和接收线路。

TMS570LC3x 不支持 QSPI、但它们支持并行模式下的多缓冲 SPI (并行 MibSPI)。 MibSPI 并行是全双工通信、但 QSPI 是半双工通信。

通信协议也不同:

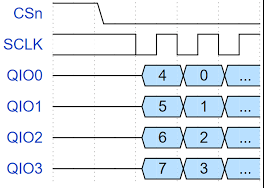

1. QSPI:以下波形表示 charlen = 8位

您可以看到、每个时钟周期传输4个位。 位顺序是 QIO0发送位4、QIO1发送位5、依此类推、在第一个时钟周期中、位0、1、3和3在第二个时钟周期中发出。

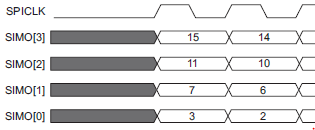

2. MibSPI 并行:以下波形表示 charlen=16位

在4数据线路模式(主控模式)中、移位寄存 器位15、11、7和3将被连接至引脚 SIMO[3]、SIMO[2]、SIMO[1]和 SIMO[0]、并且移位寄存器位12、8、4和0将被连接至引脚 SOMI[3]、SOMI[2]、SOMI[1]和 SOMI[0]。 SPICLK 的后续上升沿将移位寄存器中的数据向左移动1位(SIMO[3]将数据从位 15移位至12、SIMO[2]将数据从位11移位至8、 SIMO[1]将数据从位7移位到4、 SIMO[0]将数据从位3移位到0)。 在四个 SPICLK 周期后、当完整数据字 被传输时、移位寄存器(16位)被复制到接收缓冲区、并且 RXINT 标志将被置位。