主题中讨论的其他器件: HALCOGEN

您好!

我正在两个 TMS570LC4357控制器之间进行数据传输、两个端 MibSPI-1都与 CS0、CLK、MISO/0]、MOSI[0]和 ENA 引脚连接。 我使用代码从示例中配置 DMA。 当我在 ECONT 为4和 FCOUNT 为4的条件下进行测试时、数据传输正常。 根据我的应用要求 、将 DMA 缓冲器传输的 ECOUNT 配置为94、将 FCOUNT 配置为4。 传输最初是可以的、但在几次传输后、数据开始滚动。 我已开始使用 SPI 分析器进行检查。

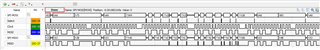

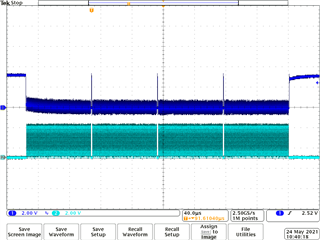

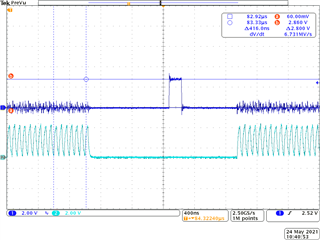

采用4x4数据的 CS 插入非常清晰、CS 是定期插入的。 对于较大的缓冲区传输、CS 看起来稍有不同、希望检查可能出现的问题。

整个缓冲区看起来是这样的。

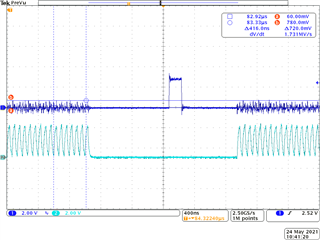

放大第一部分(有2组相同的缓冲区)

进一步缩放(每个为4个字、每个字16位)

缩放大缓冲区(有90个字、每个字16位)

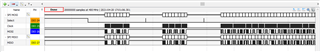

共计4+4+90+4+4+90+4+4+4+90+4+4+4+4+4+90(共计98 x 4)

CS 在较大缓冲区期间不一致、如下所示(不确定原因)

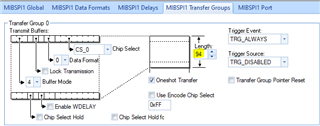

如下所示的 DMA 配置。

/*-初始化传输组*/

mibspiREG1->TGCTRL[0U]=(uint32)((uint32) 1U << 30U)//OneShot

|(UINT32)((UINT32) 0U << 29U)//pcurrent 复位

|(UINT32)((UINT32) TRG_AYeUS<< 20U)//触发事件

|(UINT32)((UINT32) TRG_DISABLED << 16U)//触发源

|(uint32)((uint32) 0U << 8U);//开始缓冲区

mibspiREG1->TGCTRL[1U]=(uint32)((uint32) 1U <<30U)//OneShot

|(UINT32)((UINT32) 0U << 29U)//pcurrent 复位

|(UINT32)((UINT32) TRG_Always << 20U)//触发事件

|(UINT32)((UINT32) TRG_DISABLED << 16U)//触发源

|(uint32)((uint32) 98U << 8U);//开始缓冲区

//MibSPI1 TG0

对于(i=0;i<3;i++)

{

mibspiRAM1->TX[i]。control =(uint16)((uint16) 5U << 13U)//缓冲模式

|(uint16)((uint16) 1U << 12U)//芯片选择保持

|(uint16)((uint16) 0U << 10U)//启用 WDELAY

|(uint16)((uint16) 0U << 11U)//锁定传输

|(uint16)((uint16) 0U << 8U)//数据格式

|((uint16)(~((uint16) 0xFFU ^(uint16) CS_0))和(uint16) 0x00FFU);//芯片选择

}

mibspiRAM1->TX[3].control =(uint16)((uint16) 5U << 13U)//缓冲模式

|(uint16)((uint16) 0U << 12U)//芯片选择保持

|(uint16)((uint16) 0U << 10U)//启用 WDELAY

|(uint16)((uint16) 0U << 8U)//数据格式

|((uint16)(~((uint16) 0xFFU ^(uint16) CS_0))和(uint16) 0x00FFU);//芯片选择

//MibSPI1 TG1

(i=4;i<7;i++)

{

mibspiRAM1->TX[i]。control =(uint16)((uint16) 5U << 13U)//缓冲模式

|(uint16)((uint16) 1U << 12U)//芯片选择保持

|(uint16)((uint16) 0U << 10U)//启用 WDELAY

|(uint16)((uint16) 0U << 11U)//锁定传输

|(uint16)((uint16) 0U << 8U)//数据格式

|((uint16)(~((uint16) 0xFFU ^(uint16) CS_0))和(uint16) 0x00FFU);//芯片选择

}

mibspiRAM1->TX[7]。control =(uint16)((uint16) 5U << 13U)//缓冲模式

|(uint16)((uint16) 0U << 12U)//芯片选择保持

|(uint16)((uint16) 0U << 10U)//启用 WDELAY

|(uint16)((uint16) 0U << 8U)//数据格式

|((uint16)(~((uint16) 0xFFU ^(uint16) CS_0))和(uint16) 0x00FFU);//芯片选择

/* TG 起始地址。 PSTARTx 存储相应 TG 的起始地址。 相应的*/

/*结束地址由后续 TG 起始地址减1 (PENDx[TXG]=*/)内在定义

/* PSTARTx[TGX+1]-1)。 在以下情况下,PSTARTx 被复制到 PCURRENTx 中:*/

for (i=0;i<8;i++)

{

tgPSTART1[i]=(mibspiREG1->TGCTRL[i]>> 8)& 0xFF;

}

在插入之前和之后、我已经为 CS 和 ENA 引脚提供了足够的延迟。

数据也是 UINT16大小的简单数组。

寻求帮助以了解问题可能是什么以及如何解决。

Chandra