我们有一个配置了480MHz PLL 频率和120MHz 系统时钟的 Tiva 129。 为了在特定时间降低功耗、我们希望将 SYSCLK 降低到低得多的值、同时保持所有其他(包括 USB)正常运行。 在此期间、我们知道 I/O 和处理器负载将大幅降低。

将 Tiva 上的 USB 用作 CDC 器件。

PLL 保持在480MHz、我们更改了 SYSDIV 和 MEMTIME0、如手册第5.3节末尾所示。 这可以根据需要工作、当从120MHz 更改为30MHz 时、我们可以看到节能效果良好、一切都很可靠。

我们希望使用更低的速率并节省更多电量。 例如、当下降至12MHz 时、USB 变得不可靠。 (我们使用的是 CDC 器件驱动程序)。 当以人类进入速率从终端仿真器输入字符时、终端仿真器中的某些字符要么未接收、要么未回显(回显是我们的代码、在所有速率下都是可靠的)。 此外、当 char 丢失时、处理器似乎卡在 USB 驱动程序中的某个位置(来自 TI)。 闪烁的 LED 指示处理器仍在运行、并且中断继续被处理。

断开(逻辑上、非物理上)和重新连接终端仿真器通常会显示一些"卡住"的输出和响应、并且还会指示有时错过了一些输入字符。 在这种情况下、重新连接在 Linux 下显示相同的器件名称、因此我们知道总线上没有发生器件重新枚举。 (在 Linux 下使用 CoolTerm)。

TIvAware USB 库自述文件指示修订版本2.1.0.12573。

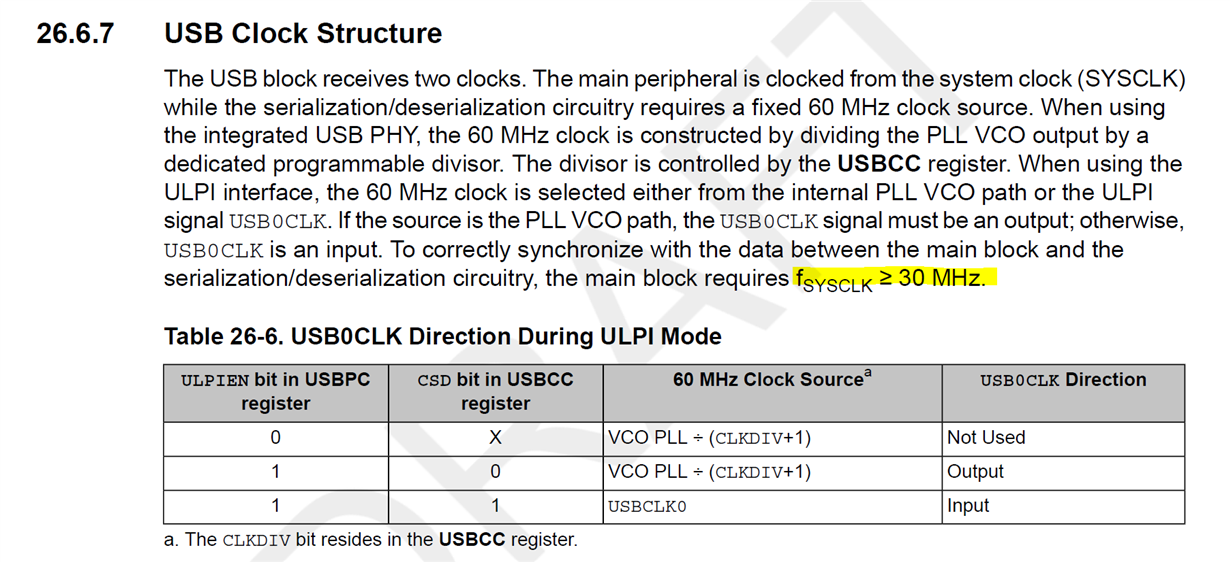

查找有关这方面或类似经验的建议、或者在使用 USB 时是否有 SYSCLK 的下限。 同样、PLL 保持在480、因此 Tiva 中的 USB 控制器应该正常。

谢谢、此致、

Tim