大家好、我们正在调试 TM4C123BE6 SSI 从程序。

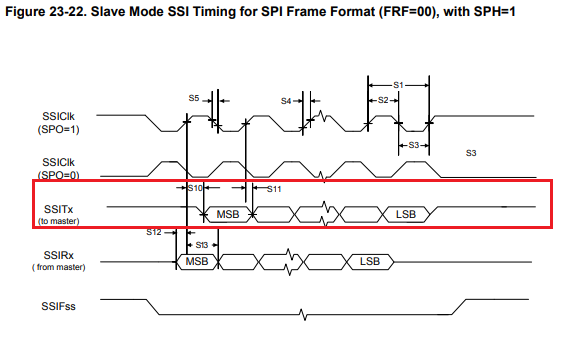

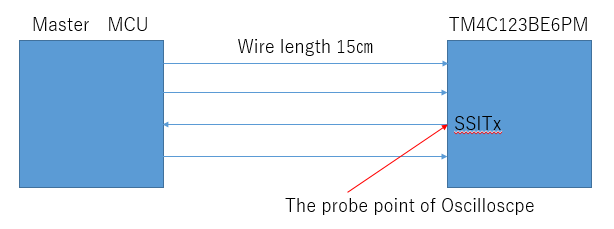

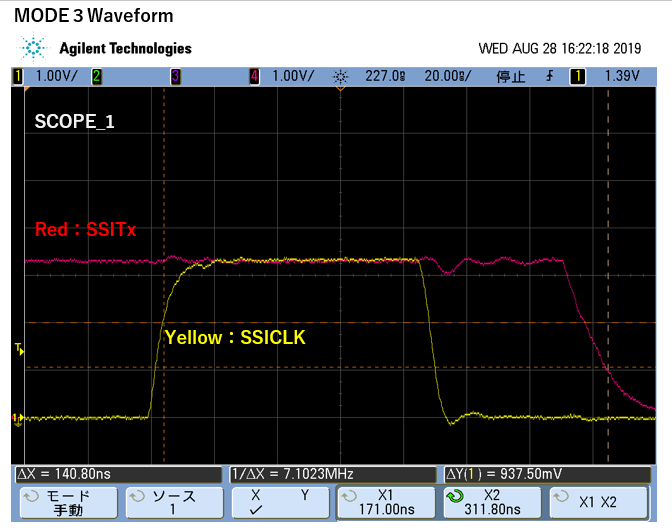

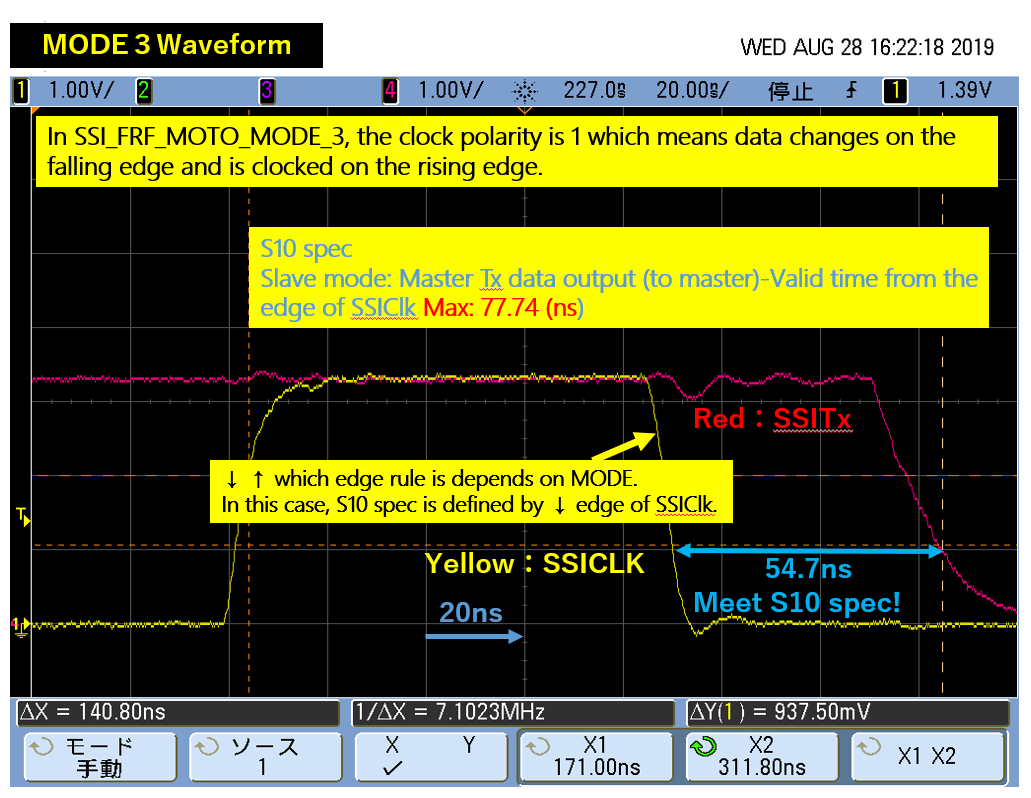

我们选择 SSI 从模式3 (SPO = 1、SPH = 1)。 但 SSITx 波形与数据表的说明有所不同(图23-22)。

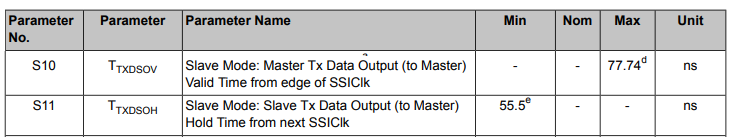

S10和 S11值如下;

我们使用以下 SSIConfigSetExpClk 函数。

SSIConfigSetExpClk (SSI0_BASE、SysCtlClockGet ()、SSI_FRF_MOTO_MOTO_MODE_3、 SSI_MODE_SLAVE、66666、 8);

我们希望使用 SSITx 来满足 MODE3 (图23-22)规格。

如果有任何额外的 S/W 设置以满足 MODE3规格、请告诉我。

此致、

ay0689_3.