Other Parts Discussed in Thread: ADC141S626

主题中讨论的其他器件:ADC141S626、 SEGGER

大家好、

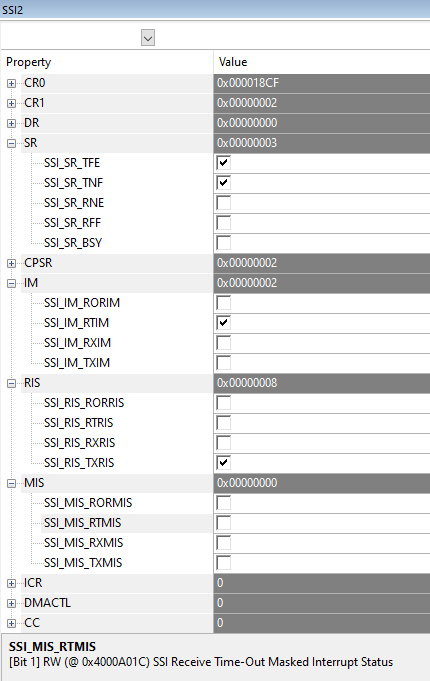

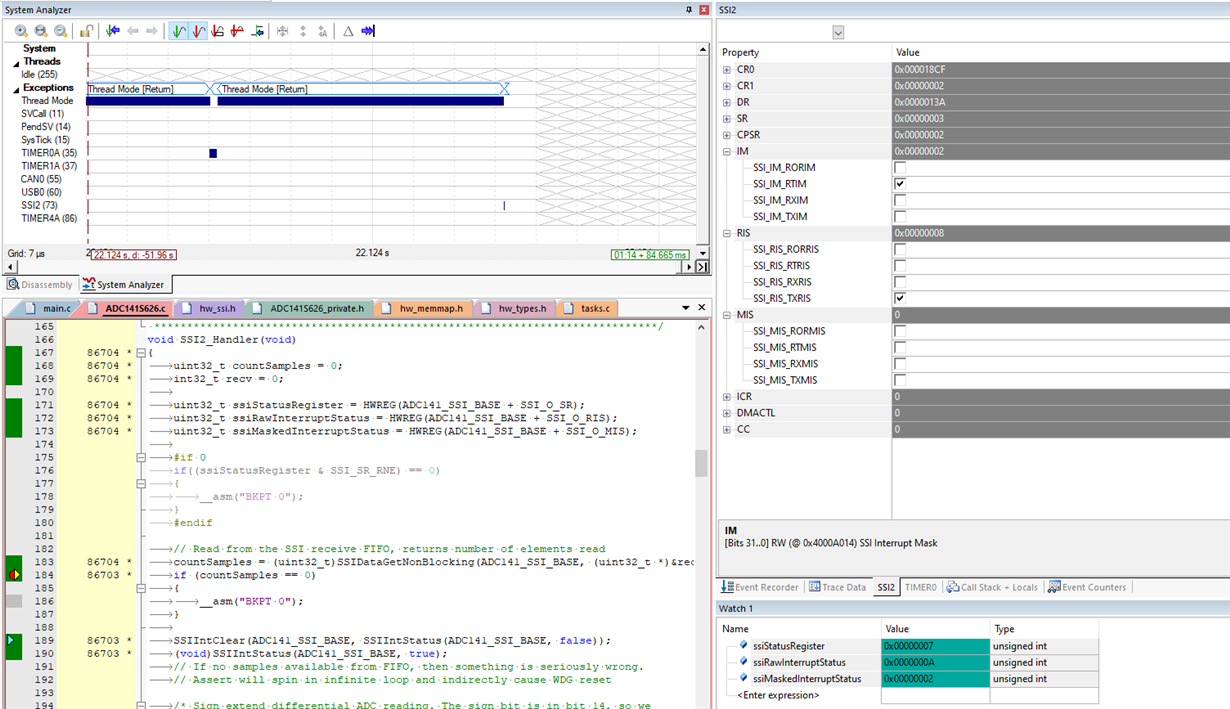

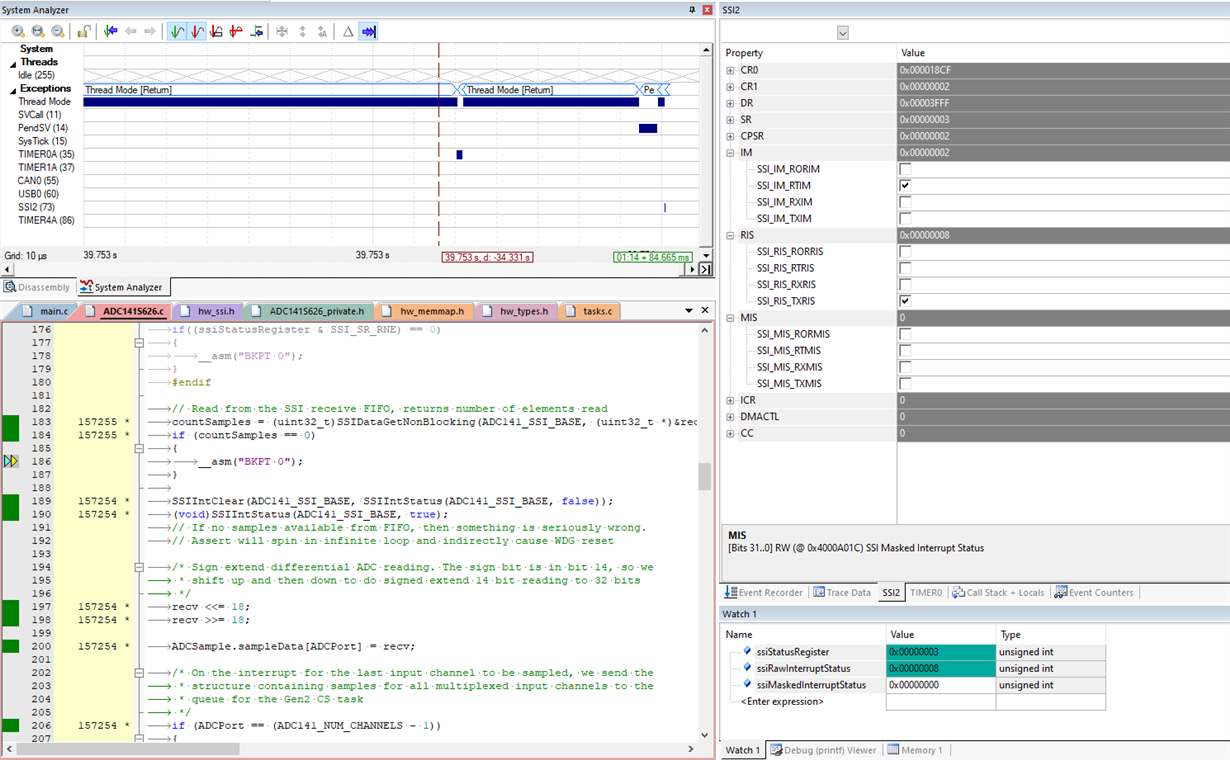

我正在尝试调试一个问题、在这个问题上、当一个接收超时中断被触发但没有数据可用时、我希望从 SSI ISR 处理程序中读取数据。 当我们读取屏蔽的中断状态时、它是0。 这应该表明没有触发中断、那么为什么处理器跳转到中断处理程序?

我们要做的是:

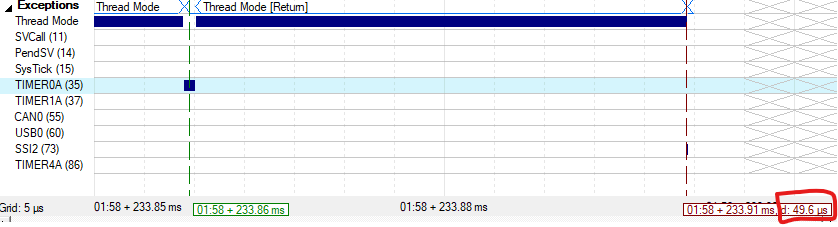

我们使用 Timer 0A 中断、使用 TivaAware SSIDataPutNonBlocking API 启动 SSI 传输。 SSI 速度设置为1MHz、接收超时中断使能、因此 SSI 中断会触发~48uS (16位 SSI + 32时钟超时)。 我可以验证调试器的计时是否按预期工作。 这个问题是随机的、我们可以毫无问题地进行上千个数据传输、然后一个数据传输将失败。 我们可以运行一个系统数天、而另一个系统只能运行几分钟。

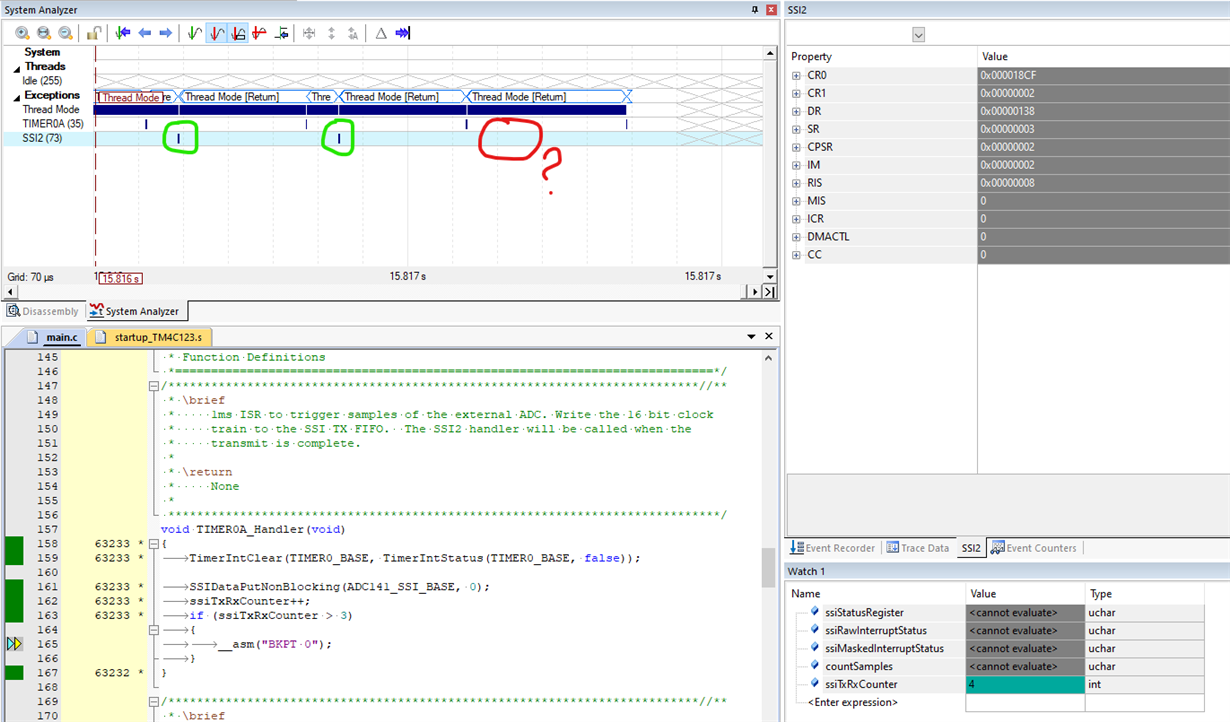

调试器屏幕截图:

相关代码片段:

#define ADC141_GPIO_Periph SYSCTL_PERIPH_GPIOH #define ADC141_PERIPh SYSCTL_PERIPH_SSI2 #define ADC141_GPIO_base GPIO_Porth_BASE #define ADC141_SSI_base SSI2_base #define ADC141_SCLK_PIN GPIO_PIN_4 #define ADC141_CS_PIN GPIO_PIN_5 #define ADC141_SDO GPIO_PIN_6 #define ADC141_GPIO_SSICLK_CFG GPIO_PH4_SSI2CLK #define ADC141_GPIO_SSIRX_CFG GPIO_PH6_SSI2RX #define ADC141_GPIO_SSICS_CFG GPIO_PH5_SSI2FSS #define ADC141_BAUD 1000000 #define ADC141_Protocol SSI_FRF_MOTO_MODE_3 #define ADC141_MODE SSI_MODE_MASTER #define ADC141_DATAWIDTH 16 /*初始化代码*/ SysCtlPeripheralEnable (ADC141_GPIO_Periph); SysCtlPeripheralEnable (ADC141_Periph); GPIOPinConfigure (ADC141_GPIO_SSICLK_CFG); GPIOPinConfigure (ADC141_GPIO_SSIRX_ICS); GPIOPinConfigure (ADC141_GPICFG_GPIO_CFG);GPIOPENCI_GPIO GPIOPinTypeSSI (ADC141_GPIO_base、ADC141_SCLK_PIN | ADC141_SDO | ADC141_CS_PIN); SSIConfigSetExpClk (ADC141_SSI_base、SysCtlClockGet ()、ADC141_Protocol、ADC141_MODE、 ADC141_BAUD、ADC141_DATAWIDTH); SSIIntEnable (ADC141_SSI_BASE、SSI_RXTO); IntPrioritySet (INT_SSI2、 0xE0); IntEnable (INT_SSI2); SSIEnable (ADC141_SSI_base); void TIMER0A_Handler (void) { TimerIntClear (TIMER0_BASE、TIMER0_BASE (TIMER0_BASE、false)); SSIDataPutNonBlocking (ADC141_SSI_BASE、 } void SSI2_Handler (void) { uint32_t countSamples = 0; Int32_t recv = 0; uint32_t ssiStatusRegister = HWREG (ADC141_SSI_base + SSI_O_SR); uint32_t ssiRawstockedStatus = HWREG (ADC141_SSI_base + SSI_RS_0 );UINT32_SSI_RUSTRIS = US_TRIS_0 (US_SS_SS_TRIS);u_TRIS_TRIS_TRIS_0)= US_TRIS_TRIS_TRIS_TRIS_0 (_TRIS_TRIS_TRIS_0_TRUS_TRIS_TRIS_TRIS_TRIS_TRIS_0_TRIS_TR //从 SSI 接收 FIFO 读取、返回读取 的元素数量 Samples =(uint32_t) SSIDataGetNonBlocking (ADC141_SSI_base、(uint32_t *)&recv); SSIIntClear (ADC141_SSI_base、SSIIntStatus (ADC141_SSI_base、false); /* snip */ }