各位专家、您好!

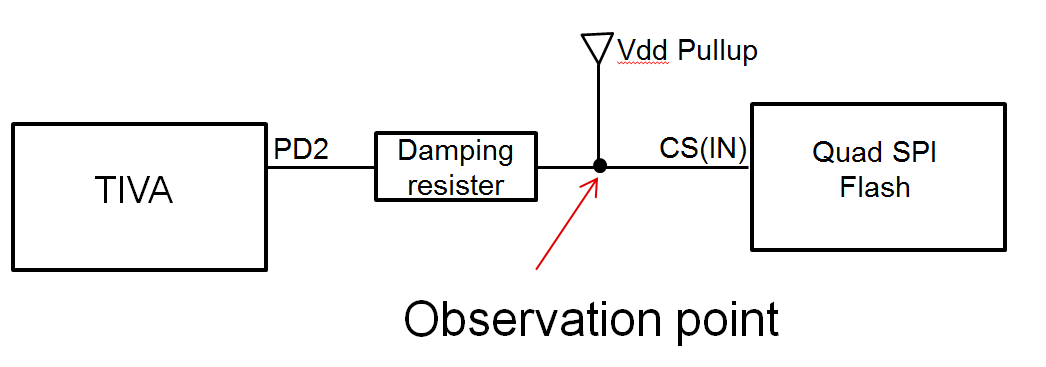

在断电过程中、我收到有关 PD2终端(GPIO 引脚)的查询。 我们的客户将 PD2配置为 GPIO/开漏、并按如下方式实现了该终端。 客户配置开漏的原因是易于实现额外的 CS (片选)。

尽管我们的客户正在使用 TM4C1290NCZAD 评估其系统、但我们的客户注意到 PD2端子在系统断电期间指示处于低电平(0V)状态。 此外、当/RST 刚刚被置为有效时、观察到这种行为。 我相信 BOR (掉电复位)似乎会发生、因为 VDD 大约为2.8V。 因此、PD2配置为默认设置。 我们是否可以让您的专家对这种行为发表意见?

此外,如果可能,您能否详细说明如何避免这种意外的低交易,请?

此致、

宫崎