主题中讨论的其他器件:LP-AM243

尊敬的 TI:

配置 HW 以检测传输结束的正确方法是什么?

传输数据后、我们 希望切换到接收模式或执行其他一些操作。

切勿过早切换、这一点很重要。

我们使用 UART FIFO 来缓冲数据、以便在 TX 操作期间减轻 CPU 的负载。

一旦 达到"可编程 FIFO 阈值"电平并且没有更多数据要放入 UART_THR 中、就会禁用中断并完成传输。

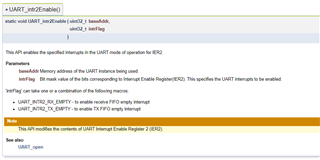

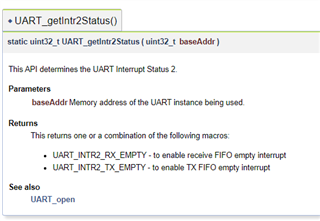

开始。 我们是否可以通过中断"空 FIFO 缓冲区和移位寄存器"进行检测、以清楚地指示所有数据已传输的时间?

UART_FCR:TX_FIFO_TRIG 配置似乎不允许设置"0空格"选项。

0h = 8个空格

1h = 16个空格

2h = 32个空格

3h = 56个空格

如果可能的话,对我来说是不干净的。

... p_serial_hw_hdl->p_params->readMode = UART_TRANSFER_MODE_CALLBACK; p_serial_hw_hdl->p_params->readReturnMode = UART_READ_RETURN_MODE_PARTIAL; p_serial_hw_hdl->p_params->writeMode = UART_TRANSFER_MODE_CALLBACK; p_serial_hw_hdl->p_params->readCallbackFxn = mbp_ti_uart_irq_rx_callback; p_serial_hw_hdl->p_params->writeCallbackFxn = mbp_ti_uart_irq_tx_callback; ... p_serial_hw_hdl->p_params->hwFlowControlThr = UART_RXTRIGLVL_56; // greater than or equal to the RX FIFO trigger level p_serial_hw_hdl->p_params->operMode = UART_OPER_MODE_13X; p_serial_hw_hdl->p_params->rxTrigLvl = UART_RXTRIGLVL_56; p_serial_hw_hdl->p_params->txTrigLvl = UART_TXTRIGLVL_56; ...

谢谢你。

此致、

ms