主题中讨论的其他器件:TM4C123AH6PM、

一段时间前、我发布了以下帖子:

https://e2e.ti.com/support/microcontrollers/tiva_arm/f/908/t/607014

这基本上从未得到答复。

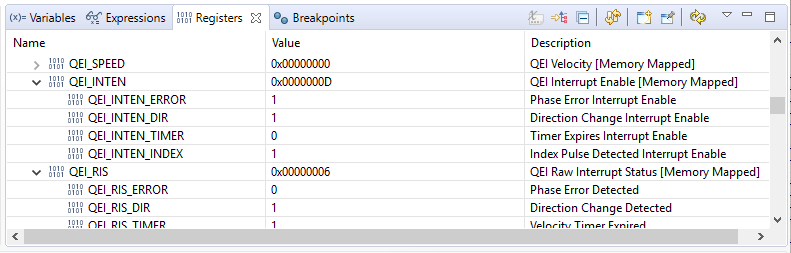

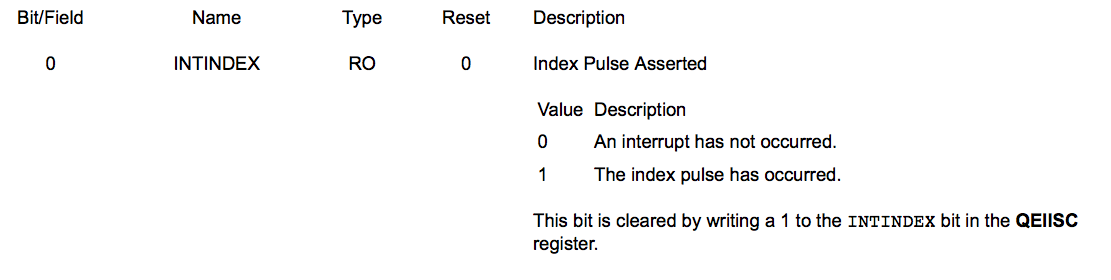

我遇到了一个永远不会生成 QEI 索引中断的问题、即 QEIRIS.INTINDEX 永远不会变为1。

这是用于初始化 QEI 和处理中断的已拆分代码:

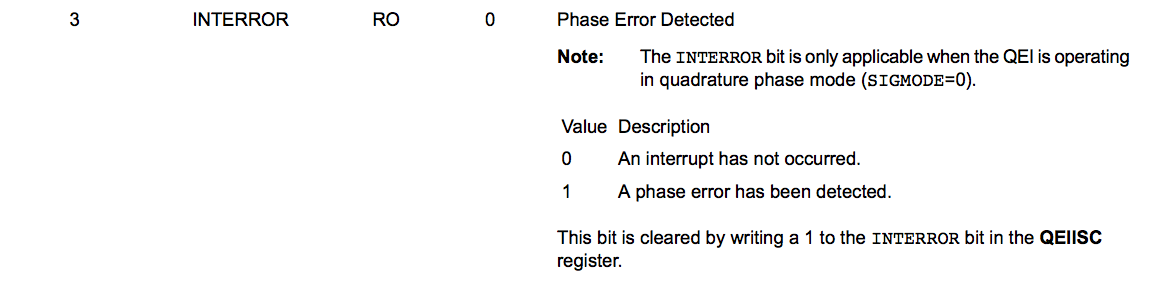

void IsrQe0Handler (void) { uint32_t 状态; 状态= MAP_QEIIntStatus (QEI0_BASE、TRUE); MAP_QEIIntClear (QEI0_BASE、状态); if (Status & QEI_INTERROR){ //处理 QEI 错误 //... } if (Status & QEI_INTINDEX){ //句柄索引脉冲 //-->如果 (Status & QEI_INTDIR){ //句柄方向更改 //... },此条件永远不会触发<--} } bIDInitQei (void) { if (!map_SysCtlPeripheralPresent (SYSCTL_Periph_QEI0) )返回 false; //重置并启用外设 map_SysCtlPeripheralDisable (SYSCEI_PERIPH_QE0); map_SysCtlPeripheralReset (SysCtl_Periptl );//将 GPIO0_GPIO0_GPIO0_GP0_GP0_GPIO0_PIN_GPIO0_GPIO0_GPIO0_GPIO0_GPIO0_GPIO0_GPIO0_GPIO0_PIN_GPIO0_GPIO0_GPIO0_GPIO0_GPIO0_GPIO0_GPIO0_GPIO0_GPIO0_GPIO0_GPIO0_GPIO0_GPIO0_GPIO0_GPIO0_GPIO0_GPIO0_GPIO0_GPIO0_GPIO0_GPIO0_GPIO0_GPIO0_GPIO0_GPIO0_GPIO0_GPIO0_GPIO0 MAP_GPIOPinTypeQEI (GPIO_PORTL_base、GPIO_PIN_2); MAP_GPIOPINTypeQEI (GPIO_PORTL_base、GPIO_PIN_3); //配置 QEI 外设 MAP_QEIConfigure (QEI0_BASE、QEI_CONFIG_CAPTURE_A_B | QECONFIG_SIMPLE_RESET_QE0);QEIV0 (QECONFIG_SION_RESET_SION_SIMP_QE0_RESET_QETOSION_SIMP_QE0_SIMP_QE0_SIMPLE_QE0_CONFIG、QE0_SIMP_QE0_QETOSION_SIMP_SIMP_SI QEI_VELDIV_1、Global. SysClockFreqHz/100); MAP_QEIVelocityEnable (QEI0_BASE); MAP_QEIEnable (QEI0_BASE); MAP_QEIIntEnable (QEI0_BASE、 (QEI_INTERROR | QEI_INTINDEX | QEI_INTDIR); MAP_IntPrioritySet (INT_QEI0、0x20); MAP_IntEnable (INT_QEI0); 返回 TRUE; }

未触发的条件为 Status = QEI_INTINDEX 、如注释中标记的那样。

我已经验证了我们的正交编码器确实在按预期产生索引脉冲、并且信号被路由到(并到达)正确的 MCU 引脚。

因此、我测试了另一种方法:

void IntGpioPortLHandler (void) { uint32_t Status; Status = GPIOIntStatus (GPIO_PORTL_base、true); GPIOIntClear (GPIO_PORTL_base、Status); 如果(状态=GPIO_INT_PIN_3){ //此条件会触发 //... } } bCtlInitQei (void) { if (!MAP_SysCtlPeripheralPresent (SYSCTL_Periph_QEI0) )返回 false; //重置并启用外设 MAP_SysCtlPeripheralDisable (SYSCEI_PERIPH_QE0);MAP_SysCtlPeripalReset (SysCtl_GPIO0_GPIO0_GP0_GP0_RESPON_GPIOR_GPIO0_GPIOR_GPIO0_GPIO0_GPIO0_GPIO0_GPIO0_GPIOR_GPIO0_GPIOR_GPIO0_RESP0_GPIO0_GPIOR_GPIO0_GPIO0_GPIO0_GPIOR_GPIO0_GPIO0_GPIO0_GPIO0_GPIOR_GPIO0_GPIO0_GPIO0_GPIOPT_GPIO0_GPIO0_GPIOPT_GPIO0_GPIO0_GPIO0_GPIOPT_GPIOPT_GPIOPT_GPIOPT_GPIO0_GPIOPT_GPIO0_GPI GPIO_PIN_2); //配置 QEI 外设 映射_QEIConfigure (QEI0_BASE、QEI_CONFIG_CAPTURE_A_B | QEI_CONFIG_NO_RESET | QEI_CONFIG_NO_SWAP、0xFFFF); MAP_QEIPositionSet (QEI0_BASE、 QEIV0);配置 QEIV0基本配置 QEI_VELDIV_1、Global. SysClockFreqHz/100); MAP_QEIVelocityEnable (QEI0_BASE); MAP_QEIEnable (QEI0_BASE); MAP_QEIIntEnable (QEI0_BASE、 (QEI_INTERROR | QEI_INTDIR)); MAP_IntPrioritySet (INT_QEI0、0x20); MAP_IntEnable (INT_QEI0); //索引引脚中断 MAP_GPIOIntClear (GPIO_PORTL_BASE、GPIO_INT_PIN_3);MAP_INT_GPIOIntType3 (GPIO_INT_INT_INT_BASE);GPIO_GPIOPTL_INT_GPIOPTL_INT_INT_INT_INT_INT_INT_INTRI GPIO_PIN_3、GPIO_RISE_EDGE); MAP_GPIOIntEnable (GPIO_PORTL_BASE、GPIO_INT_PIN_3); MAP_IntPrioritySet (INT_GPIOL、 0x20); MAP_IntEnable (INT_GPIOL); 返回 true; }

第二个代码在没有索引引脚的情况下初始化 QEI、然后将索引引脚初始化为在上升沿发生中断的 GPIO。

在此代码中、当正交编码器通过索引脉冲时、GPIO 中断会触发。

为什么 QEI 索引中断永远不会触发?