主题中讨论的其他器件:TPS74901、 LM43603

降级器、

我对 TMS570LS1114CZWTQQ1的 PLL 有疑问、详细说明如下、

在我的产品中运行一段时间后,通信异常将出现(问题时间不规则,有时几分钟,有时几小时)。

进一步的分析表明、TMS570LS1114CZWTQQ1的 PLL 故障导致看门狗脱离计时器、从而被外部看门狗复位。

外设电路:

晶体振荡器:10MHz±25ppm

1.2V LDO:1.5V 至1.2V、TPS74901

3.3V DCDC:5V 至3.3V、LM43603

看门狗:由 FPGA 实现

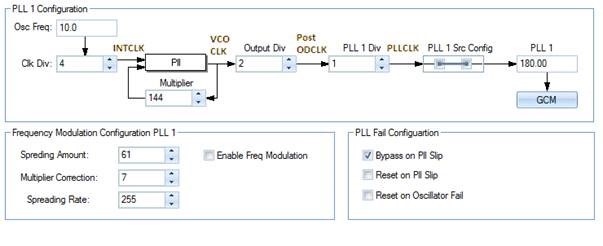

PLL 配置:

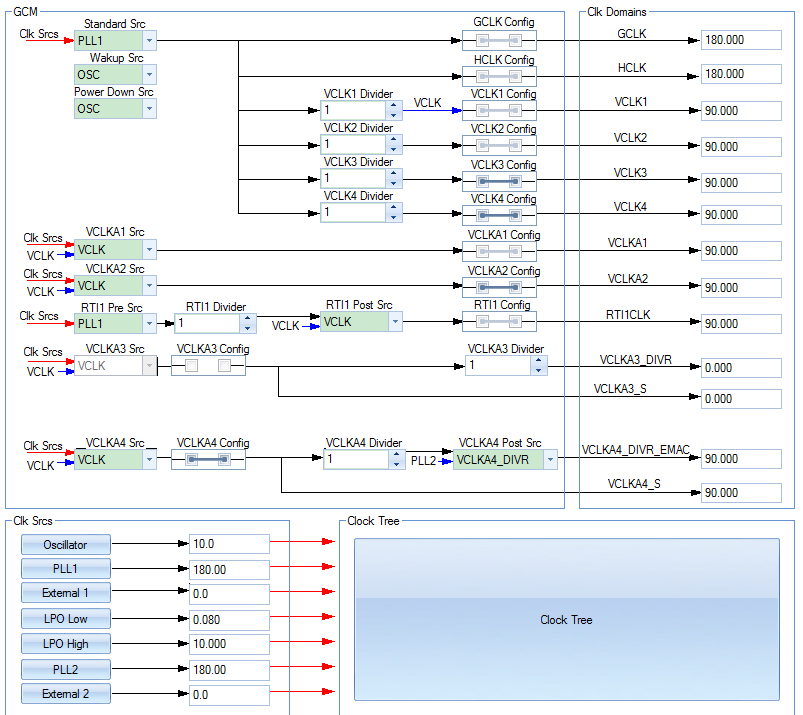

时钟配置:

我尝试使用以下方法分析问题、以供您参考:

1 μ s 屏蔽看门狗、信号、该问题在 MCU 运行一段时间后发生、此时

a) 观察由 GPIO 控制的调试指示灯的周期、发现翻转周期变长、这意味着 MCU 运行速度变慢

b) MCU 电源和外部晶体振荡器正常由示波器观察

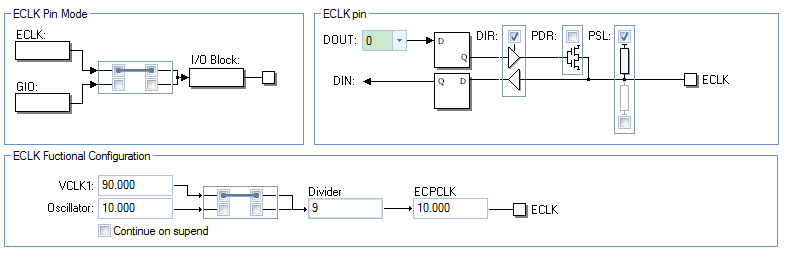

c) 然后关闭外部看门狗、MCU 的 ECLK 引脚配置为时钟输出(正常输出值 除以 VCLK1的9、即10MHz)、如下所示。 此时 ECLK 输出时钟大约为0.556MHz、因此 VCLK1时钟大约为5MHz、因此推断 PLL 输出在芯片内被旁路至10MHz。

d) 读取 GLBSTAT、FBSLIP=1 和 RFSLIP=1,

OSCFAIL = 0

其他位为0。

e) 从故障寄存器读取、未找到故障

上述行为表明 MCU 未能检测到 PLL、从而将全局时钟切换到芯片的内部时钟。 问题时间不规则,有时几分钟,有时几小时。

- 根据上述配置、PLL 的旁路功能被取消、当问题发生且此时无法读取寄存器状态时、MCU 停止运行。