主题中讨论的其他器件:EK-TM4C1294XL、 INA240、 INA282

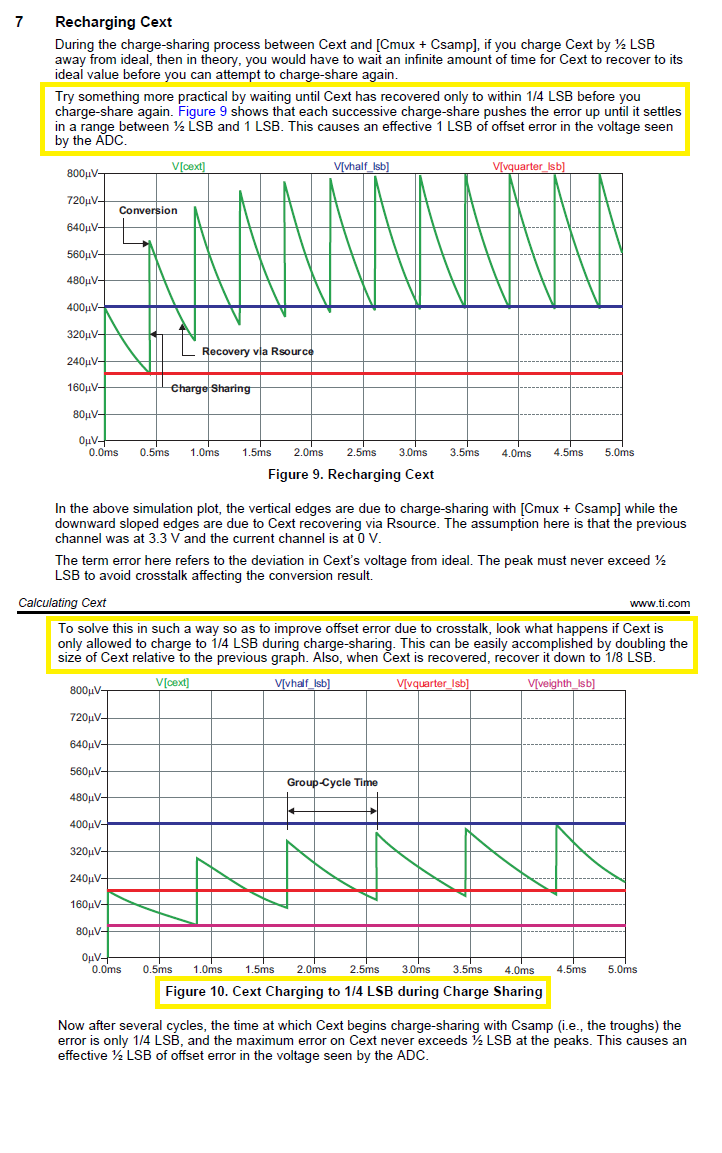

似乎 可以将 AD 转换器 稳定采集同步实时分配到 串行 FIFO 中 FIFO 时钟必须以 数字 转换器2MSPS 速率的16倍或480MHz 运行。

ADC 模块主时钟树似乎表示模拟 分频时钟(32MHz)发生 在[%N]块之后、但480MHz VCO 也应 将其传递到 FIFO 串行器的蓝色框中。

将 PLL (480/2)除以我们 的 VCO 运行240MHz 、 无法满足循环 FIFO 同步 <LSB 位到(比率指标) MSB 位 位置 的要求、因为 转换器中会进行实时稳定采集、即使是慢速周期信号也是如此。 实际上、ADC 时钟问题 表现为 实时信号采集 与尝试 处理可疑 FIFO 数据的应用不同步。 在 某些情况 下、根据模拟信号是周期性的或大部分是线性的、条件会以较大误差 INL > 3%甚至是大部分失真样本的形式进行采样。

当 SysCtrlClockFreqSet() 当前预分频 PLL/VCO 240MHz 时,我们如何使 VCO 为 ADCCLK 生成480MHz 的频率(蓝色框)? ADC 时钟似乎 是 最近发现的问题 、其触角超过了 ADC 时钟分频值。 数据表图表和文本 对于 ADC 时钟的确切分配方式都很模糊、并且因其与图15-2 单个块相关而进行了专门划分。 下面的图表似乎为 ADCCLK 可能需要480MHz 来满足 MSB 单元中的 FIFO << LSB 位的要求留下了不可避免 的可能性、因此 SAR 比率指标行为适用于所有被转换的信号、而不仅仅是较慢的稳态信号。 即使 是慢速周期信号、ADC0/1的运行方式也不正确。 它 仅将 周期性单端模拟通道样本压缩为 原始 周期性信号的缩放副本、这并不 是始终需要的行为。