请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TM4C1299KCZAD 尊敬的香榭丽舍

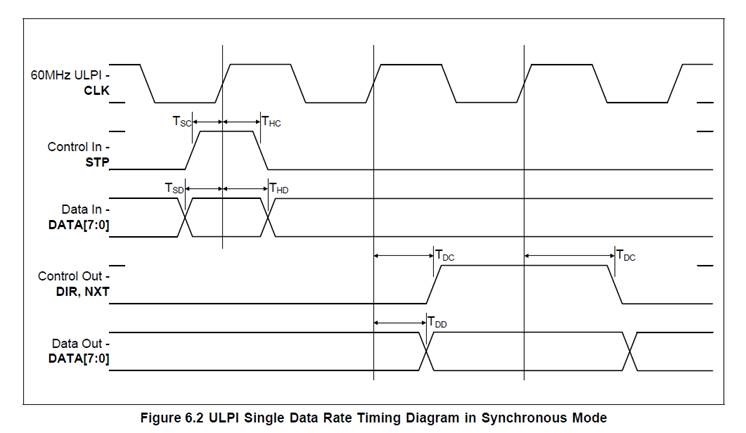

在 我们查看数据表中的 ULPI 接口时序图时、我们看到了下图:

但与 ULPI 规格似乎有所不同。

Microchip 高速 PHY USB3220C 也是不同的。

为什么我们的 ULPI 信号在时钟上升时需要延迟 U5? 而不是在时钟上升之前启动 TSC 时间?

如果您有任何建议、请随时告诉我。

非常感谢。

此致、

Janet