你好、冠军

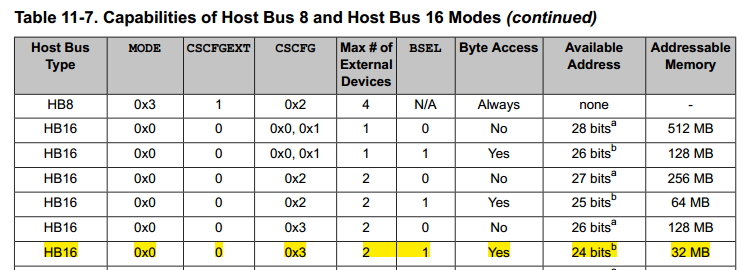

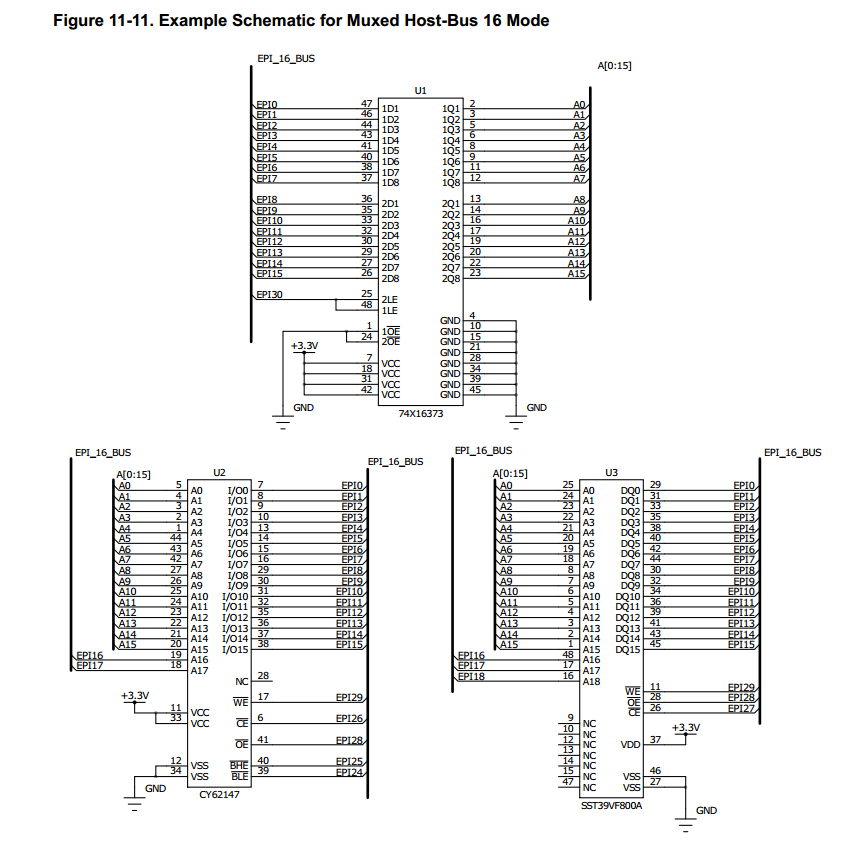

我的客户在主机总线16 ADMUX 模式下使用 M4 EPI 来访问 SRAM、他们使用了如下设置、并按如下方式进行 EPI 初始化:

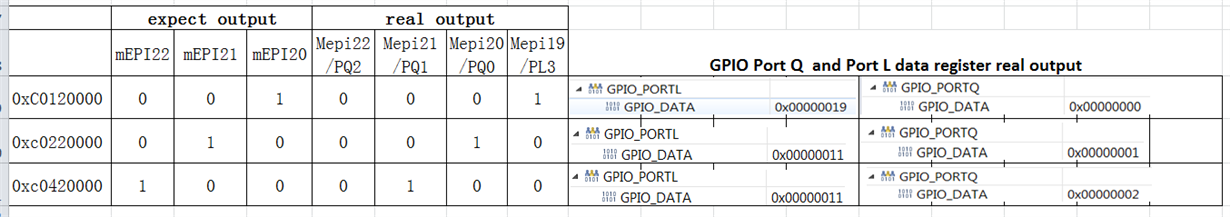

他们发现、当他们访问地址时、地址看起来需要让 shif 1位来获得正确的输出、如下所示的测试结果。

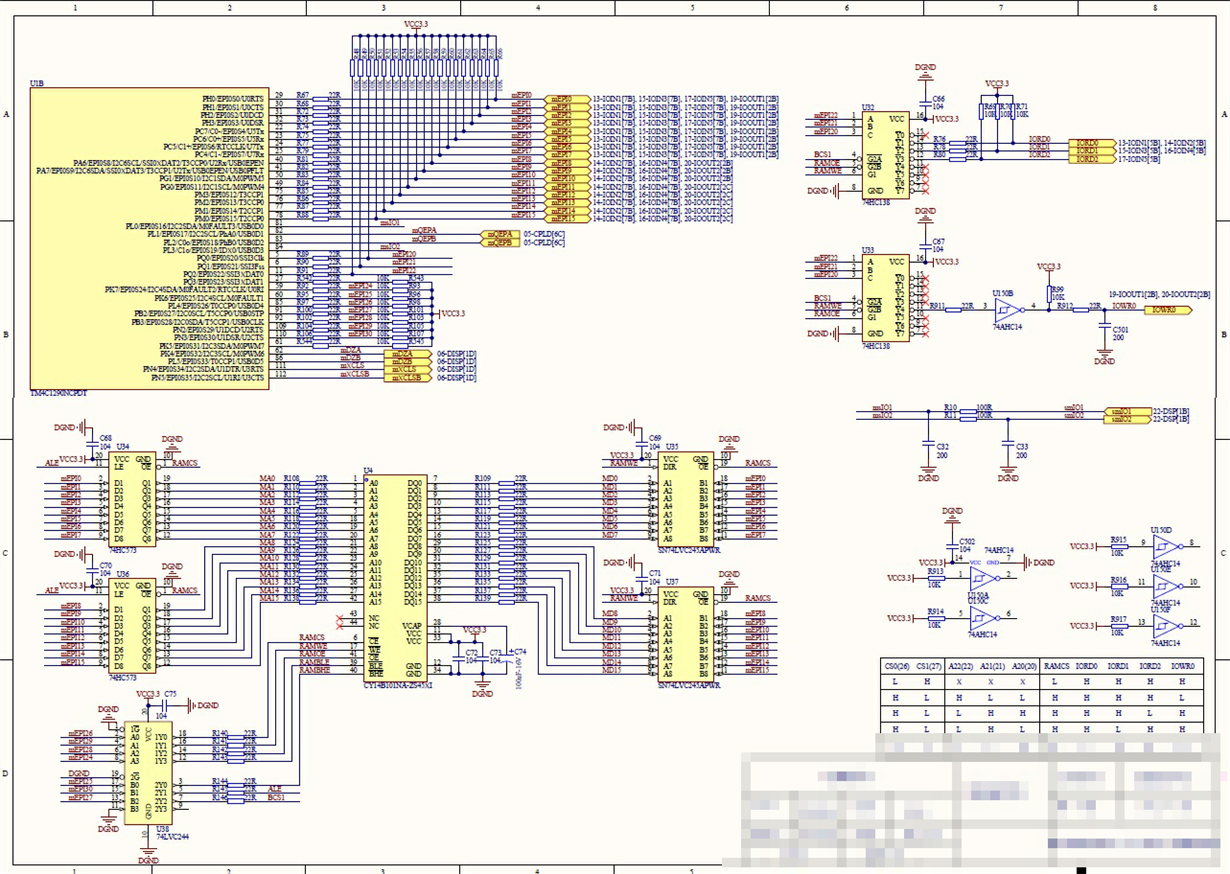

我还在 TM4C129X DK 电路板中进行测试、并获得与客户在电路板中看到的结果相同的结果。

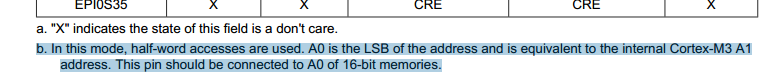

但我们在数据表中没有发现最小位地址不是 A0、因此请就问题发表意见、谢谢。

当我在 DK 电路板上进行测试时、我连接了整个项目。

void Epi_Initialize (void)(无效)

{

//启用所有 GPIO 外设。

ROM_SysCtlPeripheralEnable (SYSCTL_Periph_GPIOA);

ROM_SysCtlPeripheralEnable (SYSCTL_Periph_GPIOB);

ROM_SysCtlPeripheralEnable (SYSCTL_Periph_GPIOC);

ROM_SysCtlPeripheralEnable (SYSCTL_Periph_GPIOD);

ROM_SysCtlPeripheralEnable (SYSCTL_Periph_GPIOE);

ROM_SysCtlPeripheralEnable (SYSCTL_Periph_GPIOF);

ROM_SysCtlPeripheralEnable (SYSCTL_Periph_GPIOG);

ROM_SysCtlPeripheralEnable (SYSCTL_Periph_GPIOH);

ROM_SysCtlPeripheralEnable (SYSCTL_Periph_GPIOJ);

ROM_SysCtlPeripheralEnable (SYSCTL_Periph_GPIOK);

ROM_SysCtlPeripheralEnable (SYSCTL_Periph_GPIOL);

ROM_SysCtlPeripheralEnable (SYSCTL_Periph_GPIOM);

ROM_SysCtlPeripheralEnable (SYSCTL_Periph_GPION);

ROM_SysCtlPeripheralEnable (SYSCTL_Periph_GPIOP);

ROM_SysCtlPeripheralEnable (SYSCTL_Periph_GPIOQ);

ROM_SysCtlPeripheralEnable (SYSCTL_Periph_GPIOR);

ROM_SysCtlPeripheralEnable (SYSCTL_Periph_GPIO);

ROM_SysCtlPeripheralEnable (SYSCTL_Periph_GPIOT);

ROM_GPIOPinConfigure (GPIO_PH0_EPI0S0);

ROM_GPIOPinConfigure (GPIO_PH1_EPI0S1);

ROM_GPIOPinConfigure (GPIO_PH2_EPI0S2);

ROM_GPIOPinConfigure (GPIO_PH3_EPI0S3);

GPIOPinTypeEPI (GPIO_Porth_BASE、GPIO_PIN_0|GPIO_PIN_1|GPIO_PIN_2|GPIO_PIN_3);

ROM_GPIOPinConfigure (GPIO_PC7_EPI0S4);

ROM_GPIOPinConfigure (GPIO_PC6_EPI0S5);

ROM_GPIOPinConfigure (GPIO_PC5_EPI0S6);

ROM_GPIOPinConfigure (GPIO_PC4_EPI0S7);

GPIOPinTypeEPI (GPIO_PORTC_BASE、GPIO_PIN_7|GPIO_PIN_6|GPIO_PIN_5|GPIO_PIN_4);

ROM_GPIOPinConfigure (GPIO_PA6_EPI0S8);

ROM_GPIOPinConfigure (GPIO_PA7_EPI0S9);

GPIOPinTypeEPI (GPIO_Porta_base、GPIO_PIN_6|GPIO_PIN_7);

ROM_GPIOPinConfigure (GPIO_PG1_EPI0S10);

ROM_GPIOPinConfigure (GPIO_PG0_EPI0S11);

GPIOPinTypeEPI (GPIO_PORTG_base、GPIO_PIN_1|GPIO_PIN_0);

ROM_GPIOPinConfigure (GPIO_PM3_EPI0S12);

ROM_GPIOPinConfigure (GPIO_PM2_EPI0S13);

ROM_GPIOPinConfigure (GPIO_PM1_EPI0S14);

ROM_GPIOPinConfigure (GPIO_PM0_EPI0S15);

GPIOPinTypeEPI (GPIO_PORTM_BASE、GPIO_PIN_3|GPIO_PIN_2|GPIO_PIN_1_GPIO_PIN_0);

ROM_GPIOPinConfigure (GPIO_PQ0_EPI0S20);

ROM_GPIOPinConfigure (GPIO_PQ1_EPI0S21);

ROM_GPIOPinConfigure (GPIO_PQ2_EPI0S22);

GPIOPinTypeEPI (GPIO_PORTQ_BASE、GPIO_PIN_0|GPIO_PIN_1_|GPIO_PIN_2);

ROM_GPIOPinConfigure (GPIO_PK7_EPI0S24);

ROM_GPIOPinConfigure (GPIO_PK6_EPI0S25);

GPIOPinTypeEPI (GPIO_PORTK_base、GPIO_PIN_7|GPIO_PIN_6);

ROM_GPIOPinConfigure (GPIO_PL4_EPI0S26);

GPIOPinTypeEPI (GPIO_PORTL_BASE、GPIO_PIN_4);

ROM_GPIOPinConfigure (GPIO_PB2_EPI0S27);

ROM_GPIOPinConfigure (GPIO_PB3_EPI0S28);

GPIOPinTypeEPI (GPIO_PORTB_BASE、GPIO_PIN_2|GPIO_PIN_3);

ROM_GPIOPinConfigure (GPIO_PN2_EPI0S29);

ROM_GPIOPinConfigure (GPIO_PN3_EPI0S30);

GPIOPinTypeEPI (GPIO_PORTN_BASE、GPIO_PIN_2|GPIO_PIN_3);

ROM_SysCtlPeripheralEnable (SYSCTL_Periph_EPI0);

ROM_EPImodeSet (EPI0_BASE、EPI_MODE_HB16);

ROM_EPIConfigHB16Set (EPI0_BASE、EPI_HB16_CSCFG_ALE_DUAL_CS、0xff);

ROM_EPIDividerCSSet (EPI0_BASE,0,2); //除以4,30Mhz,SDRAM

ROM_EPIDividerCSSet (EPI0_BASE、1、2);

//ROM_EPIDividerCSSet (EPI0_BASE,1,118); //除以120,1MHz,IO

ROM_EPIConfigHB16CSSet (EPI0_BASE、0、EPI_HB16_MODE_ADMUX | EPI_HB16_ALE_HIGH | EPI_HB16_BSEL | 0x0000FF00);

ROM_EPIConfigHB16CSSet (EPI0_BASE、1、EPI_HB16_MODE_ADMUX | EPI_HB16_ALE_HIGH | EPI_HB16_BSEL | 0x07000000);

ROM_EPIConfigHB16TimingSet (EPI0_BASE、0、EPI_HB16_PSRAM_256 | EPI_HB16_CAP_WIDTH_2);

ROM_EPIConfigHB16TimingSet (EPI0_BASE、1、EPI_HB16_PSRAM_256 | EPI_HB16_CAP_WIDTH_2);

ROM_EPIAddressMapSet (EPI0_BASE、

(EP_ADDR_CODE_SIZE_256B|

EPI_ADDR_CODE_BASE_NONE |

EPI_ADDR_PER_SIZE 16MB |

EPI_ADDR_PER_BASE_C|

EPI_ADDR_RAM_SIZE 256B|

EPI_ADDR_RAM_BASE_NONE

)

);

}